# the application of linear microcircuits volume 1

london milan münich paris singapore stockholm

### THE APPLICATION OF LINEAR MICROCIRCUITS

by the Applications Engineering Staff of SGS

### **CONTENTS**

| Section | 1                                                  | INTRODUCTION                                                                                                                                              |         | 2.6                                     | Summary of µA709 performance                                                                                                                                                                                       |  |

|---------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|         | 1.1                                                | Purpose of Handbook                                                                                                                                       |         | 2.6.1                                   | Main characteristics of the µA709 integrated amplifier                                                                                                                                                             |  |

|         | 1.2                                                | Instructions for Handbook usage                                                                                                                           |         | 2.6.2                                   | General circuit precautions                                                                                                                                                                                        |  |

|         | 1.3                                                | Economics of integrated circuits compared with discrete component circuits                                                                                |         | <b>2.7</b> .1 2.7.2                     | Description of µA710 circuit operation Introduction The circuit                                                                                                                                                    |  |

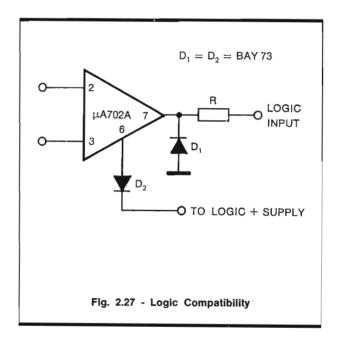

|         |                                                    |                                                                                                                                                           |         | 2.8<br>2.8.1<br>2.8.2<br>2.8.3<br>2.8.4 | Summary of µA710 performance Tabulated performance Specification of operation Description of performance Logic compatibility                                                                                       |  |

| Section | 2                                                  | DESIGNS FOR MONOLITHIC<br>LINEAR INTEGRATED CIRCUITS                                                                                                      |         | 2.9                                     | Description of $\mu$ A711 circuit operation                                                                                                                                                                        |  |

|         | <b>2.1</b> 2.1.1                                   | Design Philosophy Integrated circuits compared with discrete components                                                                                   |         | 2.9.1<br>2.9.2                          | Introduction<br>Device description                                                                                                                                                                                 |  |

|         | 2.1.2                                              | Integrated circuit solutions for obtaining specific circuit functions                                                                                     |         |                                         | Summary of $\mu$ A711 performance Performance description                                                                                                                                                          |  |

|         | <b>2.2</b> 2.2.1                                   | <b>Definitions of commonly-used terms</b> Terms applicable to operational amplifiers                                                                      |         | 2.10.2                                  | Logic compatibility                                                                                                                                                                                                |  |

|         | 2.2.2                                              | Terms applicable to voltage comparators                                                                                                                   | Section | 3                                       | LINEAR INTEGRATED CIRCUIT APPLICATIONS                                                                                                                                                                             |  |

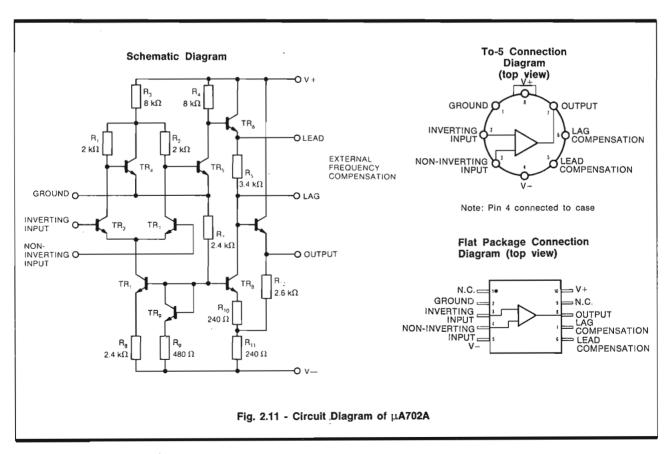

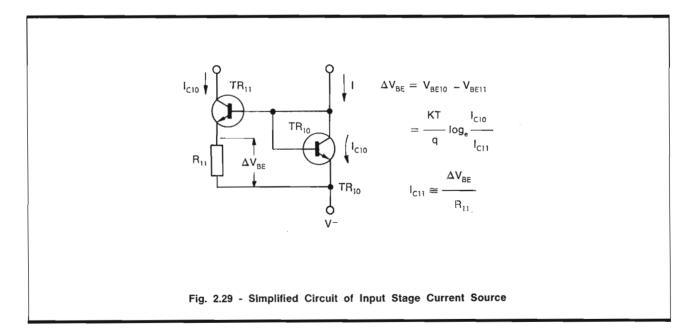

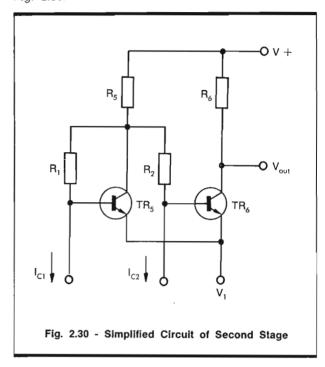

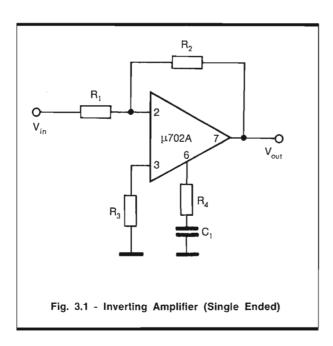

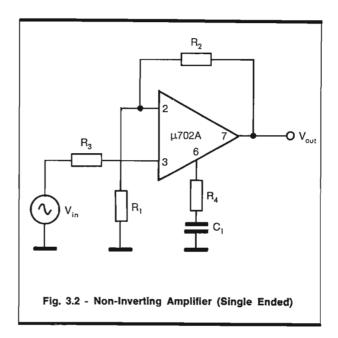

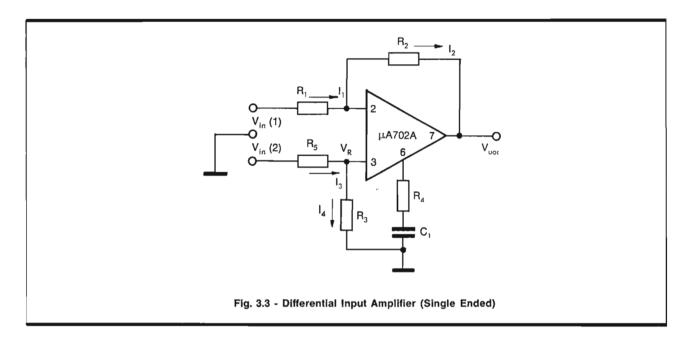

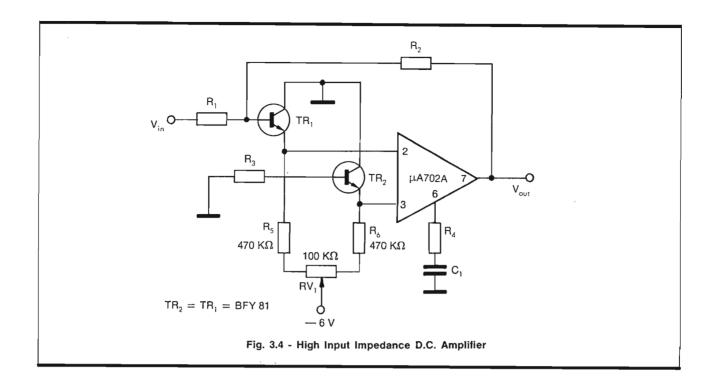

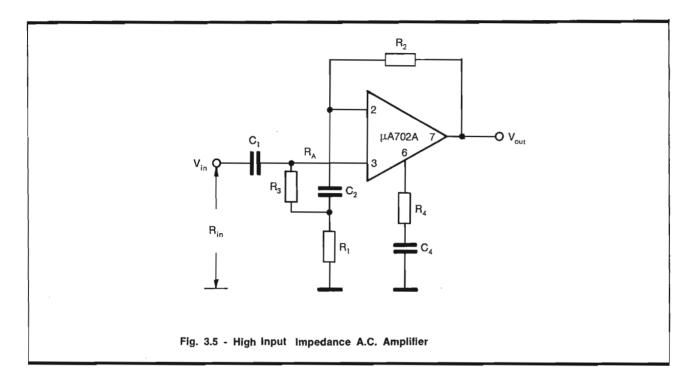

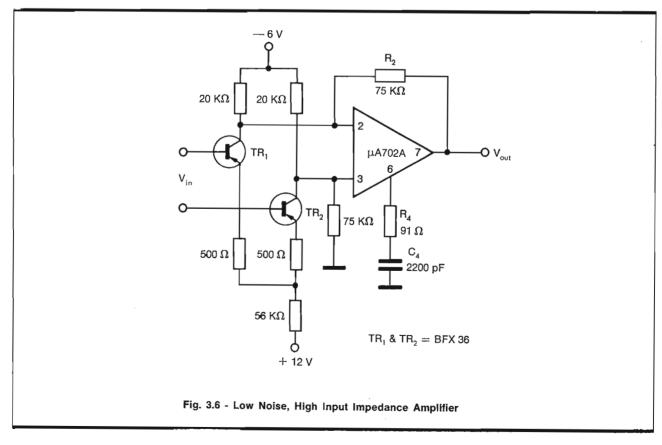

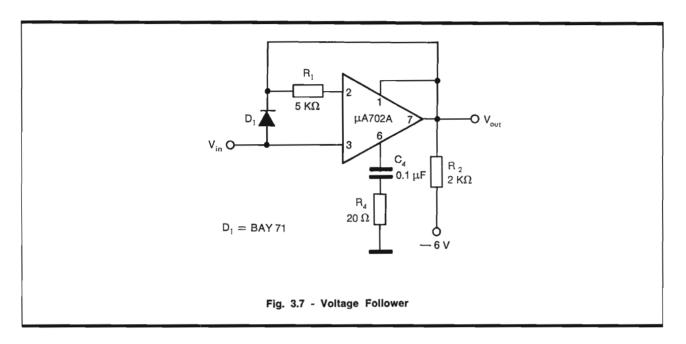

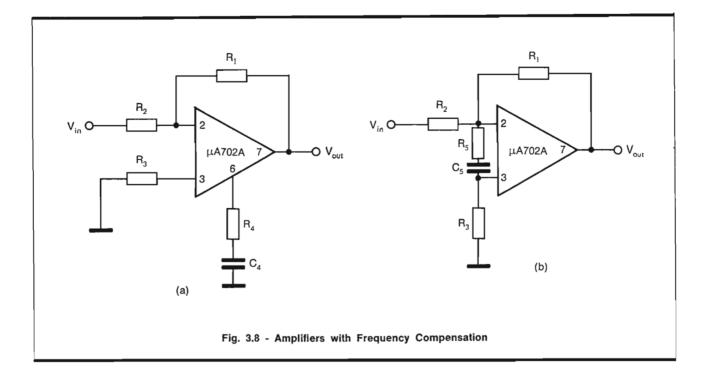

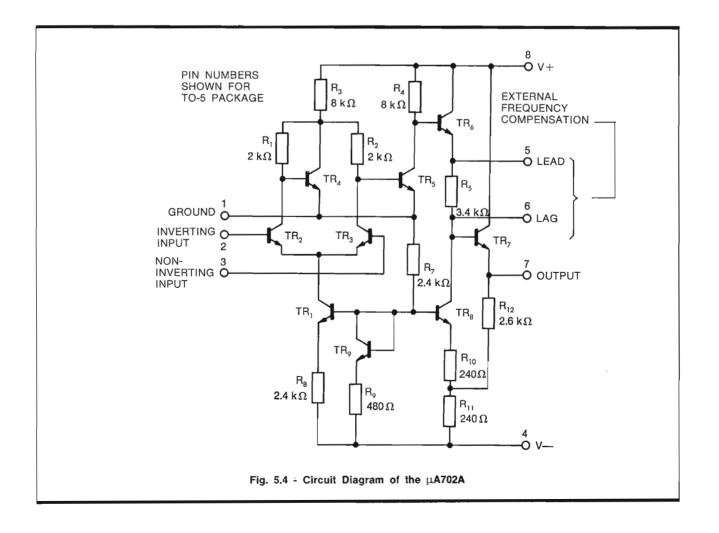

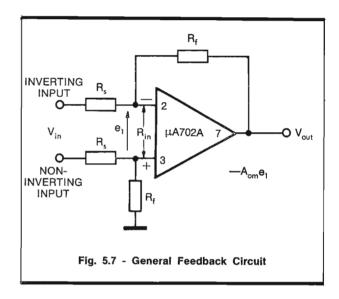

|         | 2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6 | Description of µA702A circuit operation Introduction Input stage Second stage Output stage Conditions for D.C. balance D.C. offset and component matching |         |                                         | μA702A basic amplifier circuits Inverting amplifier (single-ended) Non-inverting amplifier (single-ended Differential input amplifier (single-ended) High input impedance D.C. amplifier High input impedance A.C. |  |

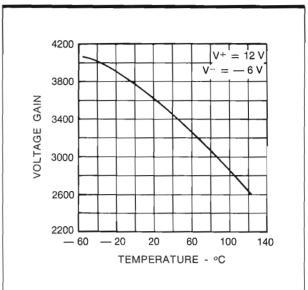

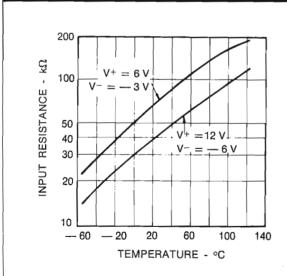

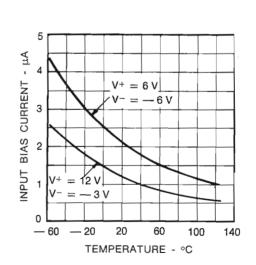

|         |                                                    | Summary of µA702A performance Amplifier basic characteristics Prevention of input latch-up conditions                                                     |         | 3.1.7                                   | amplifier Low-noise, high input impedance amplifier Voltage-follower Amplifiers with frequency                                                                                                                     |  |

|         | 2.4.3                                              | General circuit precautions                                                                                                                               |         |                                         | compensation                                                                                                                                                                                                       |  |

|         | <ul><li>2.5</li><li>2.5.1</li><li>2.5.2</li></ul>  | Description of $\mu$ A709 circuit operation Introduction Input stage                                                                                      |         | 3.1.10                                  | Amplifiers with offset voltage balancing High output-current amplifier Low-pass amplifier                                                                                                                          |  |

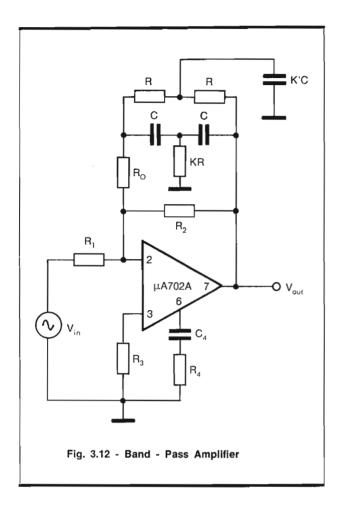

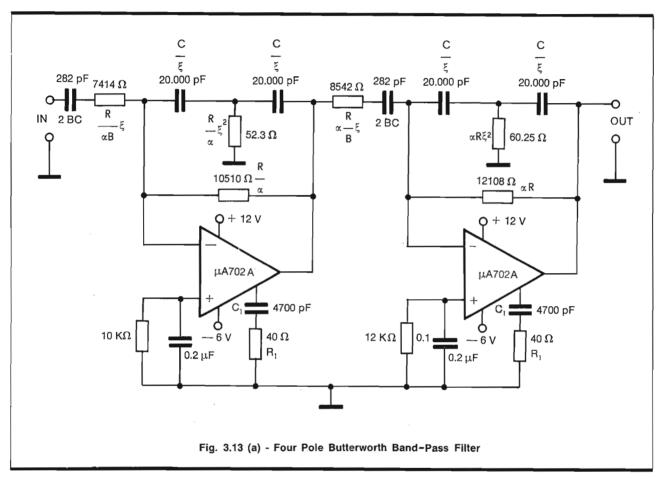

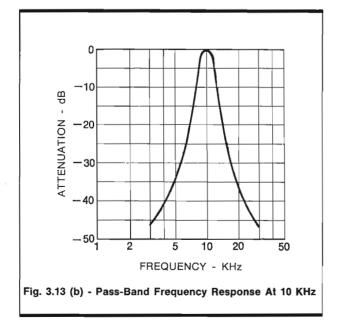

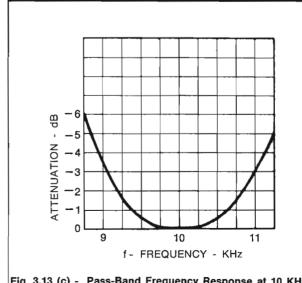

|         | 2.5.3                                              | Second stage Output stage                                                                                                                                 |         | 3.1.12                                  | Band-pass amplifier Band-pass active filter                                                                                                                                                                        |  |

| 3.2                                                                                                                                                                      | μΑ702A miscellaneous circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                |         | 3.7                                                                                                  | μA711 basic circuits                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

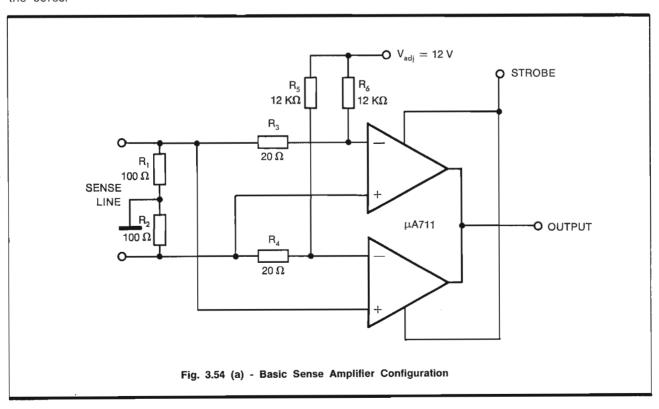

| 3.2.1                                                                                                                                                                    | Thermo-couple amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | 3.7.1                                                                                                | Sense amplifier circuits                                                                                                                                                                                                                                                                                                                                                            |

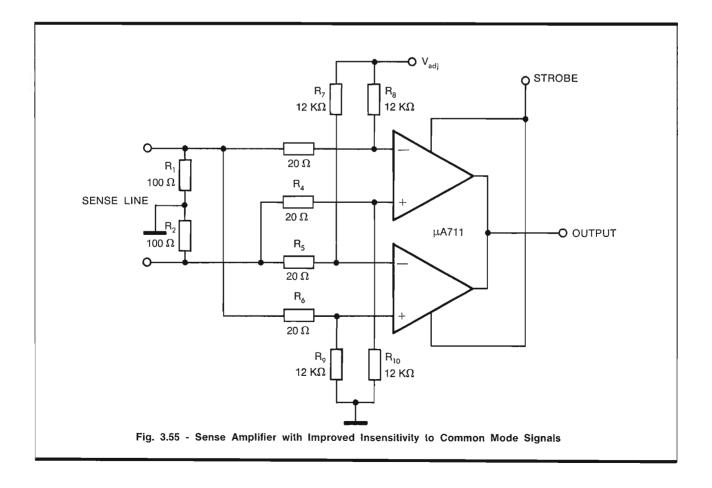

| 3.2.2                                                                                                                                                                    | Resistance bridge amplifier (thermistor bridge)                                                                                                                                                                                                                                                                                                                                                                                                                              |         | 3.7.2                                                                                                | Sense amplifier with improved insensitivity to common-mode                                                                                                                                                                                                                                                                                                                          |

| 3.2.3                                                                                                                                                                    | Piezo-electric transducer amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |                                                                                                      | signals                                                                                                                                                                                                                                                                                                                                                                             |

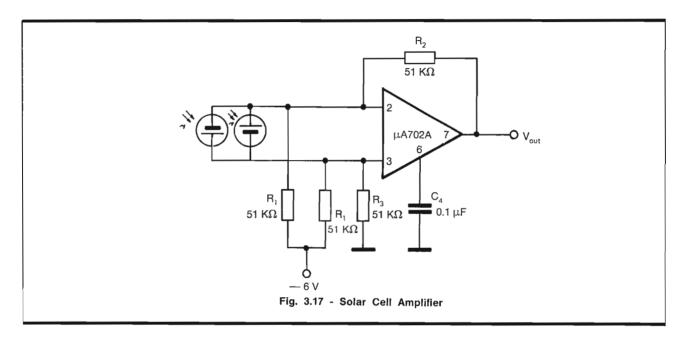

|                                                                                                                                                                          | Solar-cell amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         | 3.7.3                                                                                                | Sense amplifier circuit using                                                                                                                                                                                                                                                                                                                                                       |

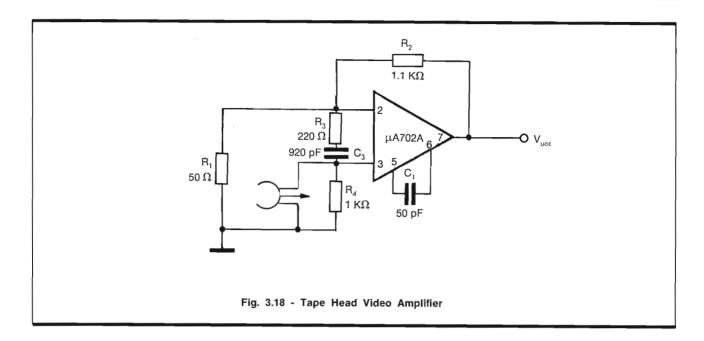

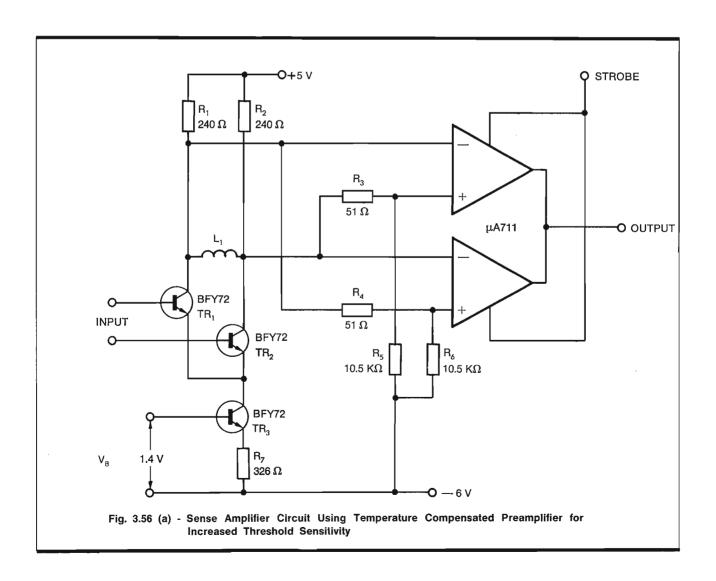

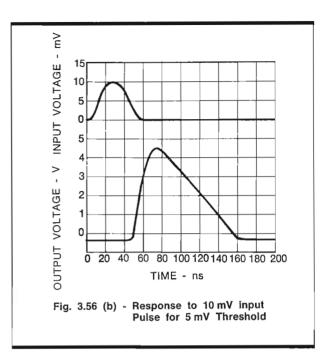

|                                                                                                                                                                          | Tape-head video amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |                                                                                                      | temperature-compensated                                                                                                                                                                                                                                                                                                                                                             |

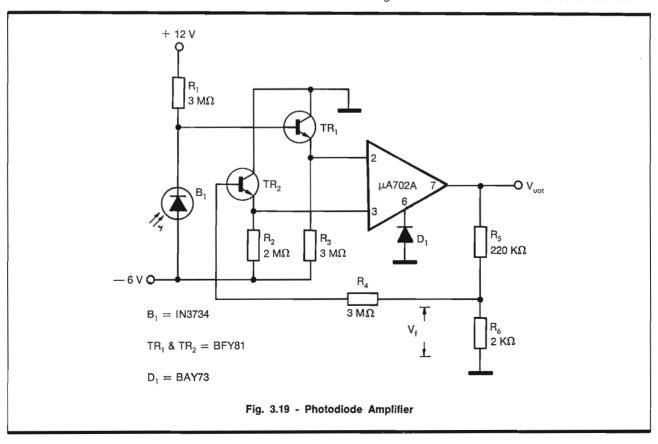

|                                                                                                                                                                          | Photo-diode amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |                                                                                                      | preamplifier                                                                                                                                                                                                                                                                                                                                                                        |

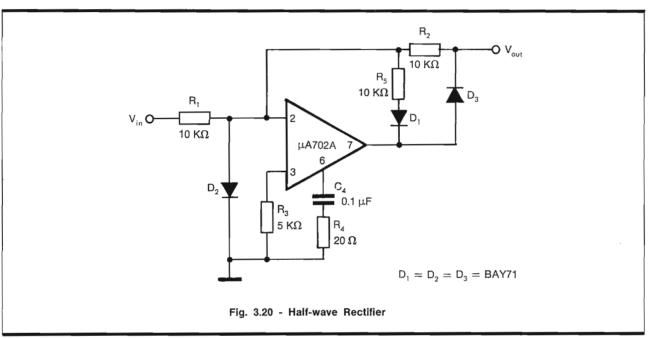

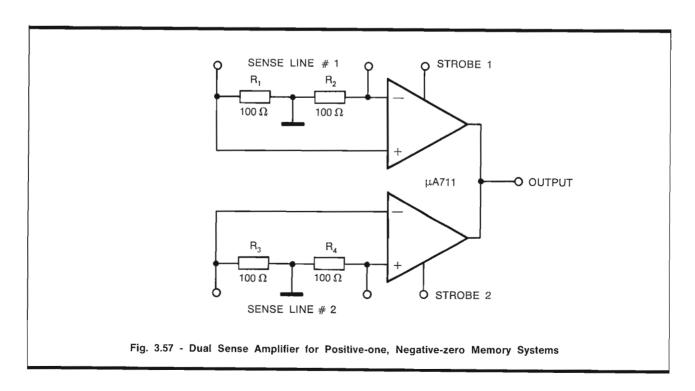

|                                                                                                                                                                          | Half-wave rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 3.7.4                                                                                                | Dual sense amplifier for                                                                                                                                                                                                                                                                                                                                                            |

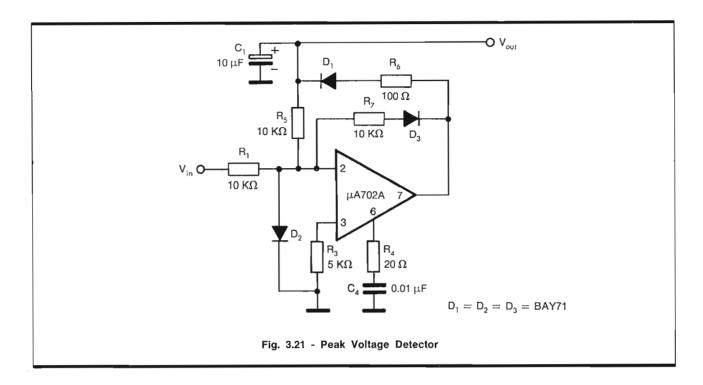

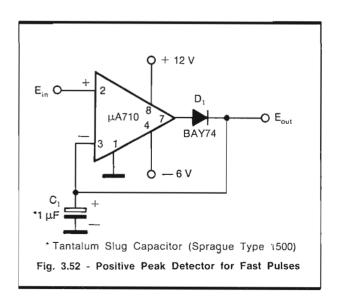

|                                                                                                                                                                          | Peak detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |                                                                                                      | positive-one, negative-zero                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |                                                                                                      | memory systems                                                                                                                                                                                                                                                                                                                                                                      |

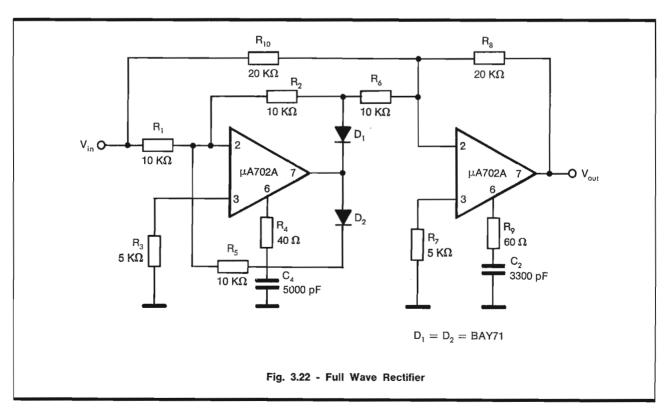

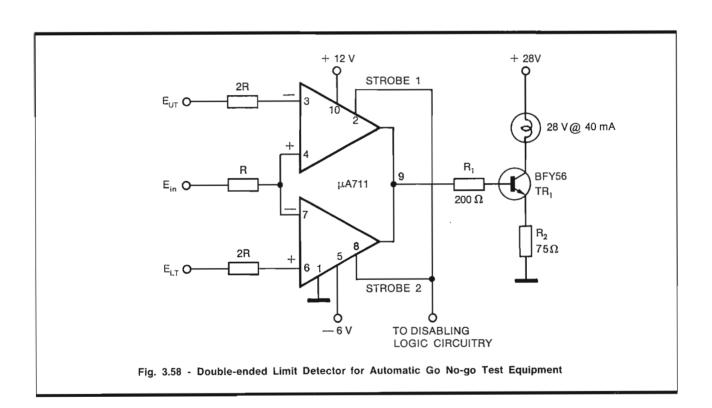

|                                                                                                                                                                          | Full-wave rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 3.7.5                                                                                                | Doubled-ended limit detector                                                                                                                                                                                                                                                                                                                                                        |

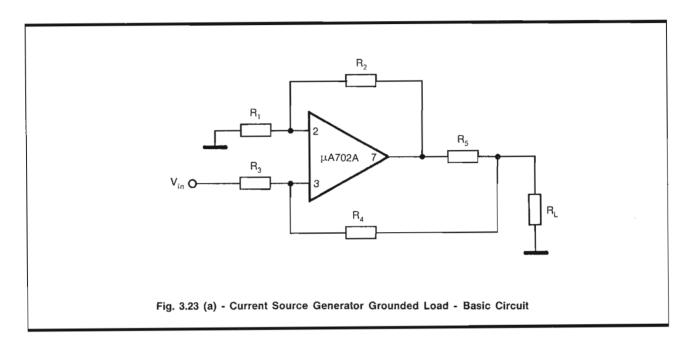

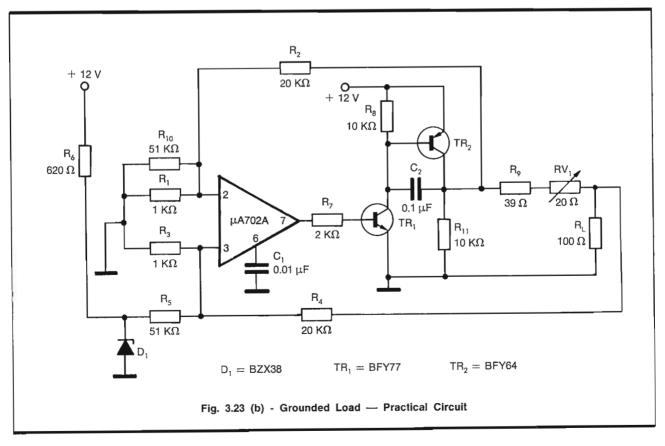

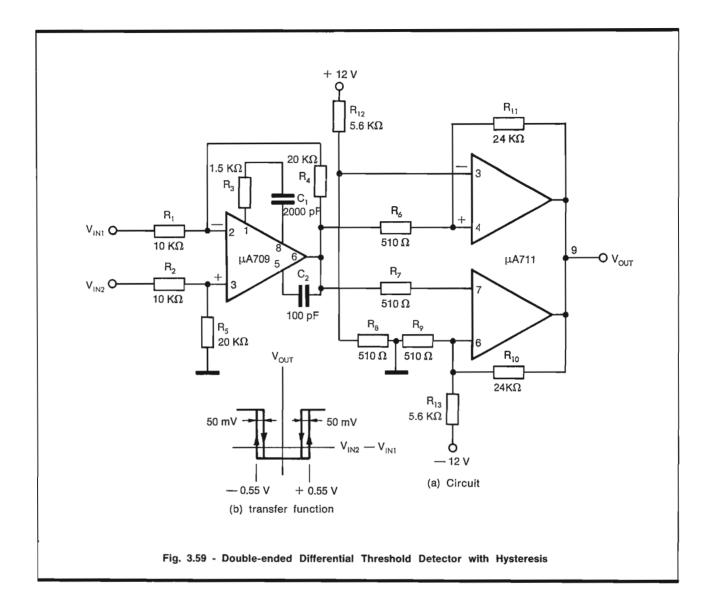

|                                                                                                                                                                          | Current source generators                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         | 3.7.6                                                                                                | Double-ended differential threshold                                                                                                                                                                                                                                                                                                                                                 |

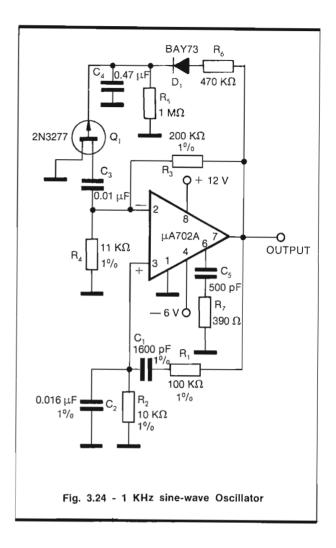

|                                                                                                                                                                          | Sine - wave oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                                                      | detector with hysteresis                                                                                                                                                                                                                                                                                                                                                            |

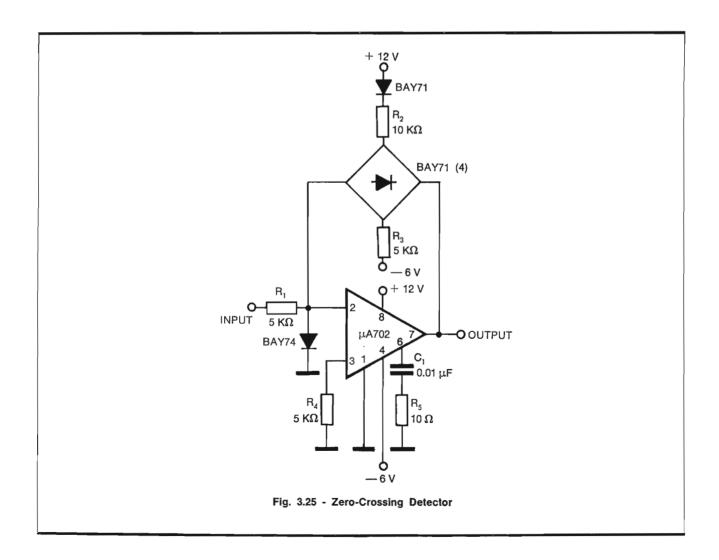

|                                                                                                                                                                          | Zero-crossing detector                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                     |

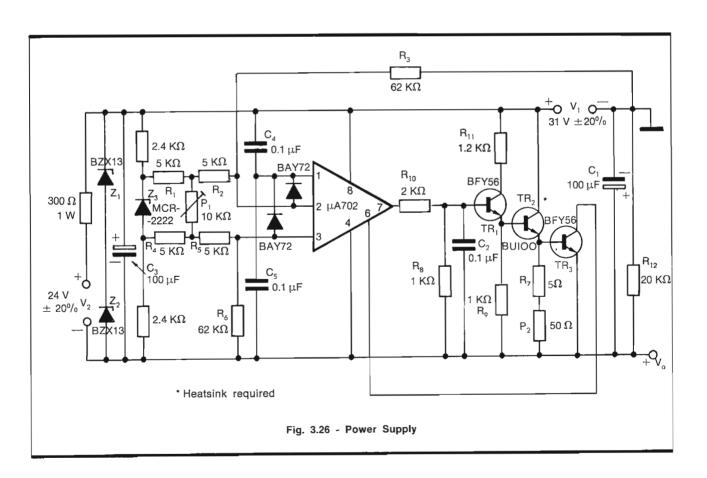

|                                                                                                                                                                          | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                     |

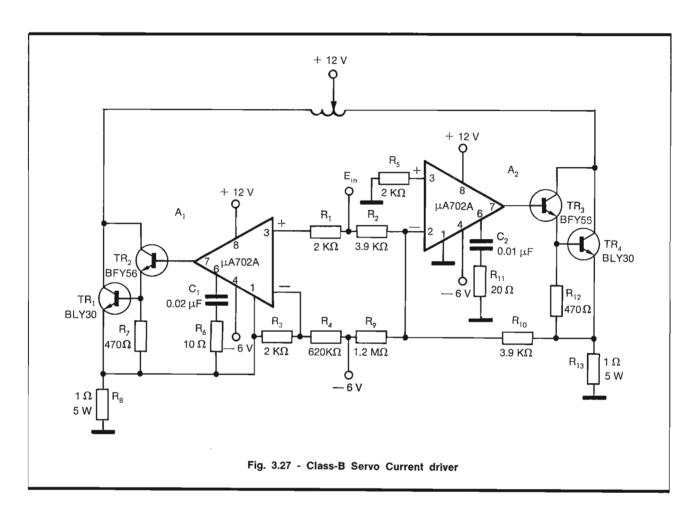

|                                                                                                                                                                          | Servo current driver                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Section | 4                                                                                                    | MEASUREMENT OF INTEGRATED                                                                                                                                                                                                                                                                                                                                                           |

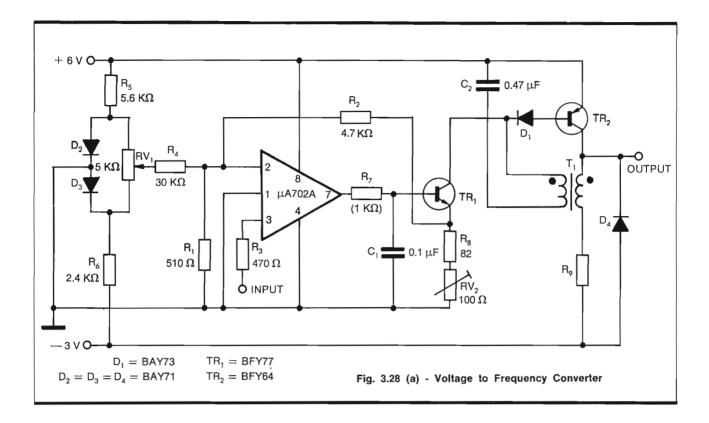

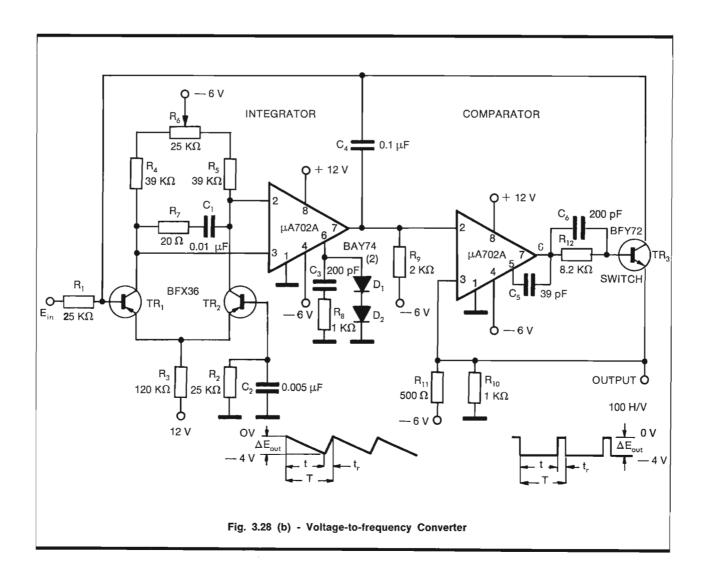

|                                                                                                                                                                          | Voltage-to-frequency converter                                                                                                                                                                                                                                                                                                                                                                                                                                               | Section | 4                                                                                                    | CIRCUIT BASIC PARAMETERS                                                                                                                                                                                                                                                                                                                                                            |

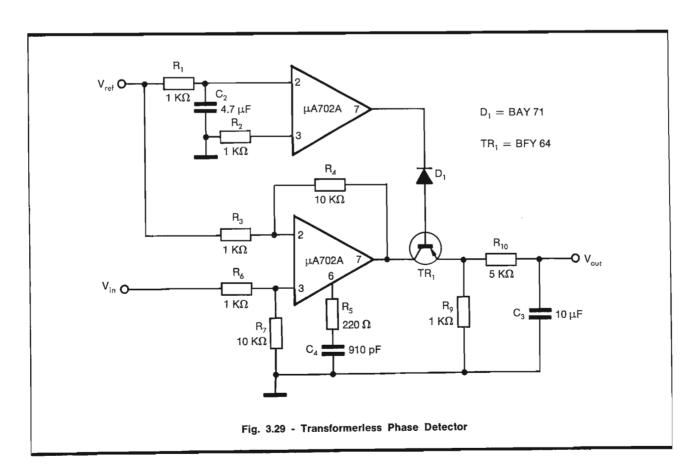

| 3.2.16                                                                                                                                                                   | Transformerless phase detector                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |                                                                                                      | CIRCUIT BASIC FARAMETERS                                                                                                                                                                                                                                                                                                                                                            |

| 3.3                                                                                                                                                                      | μΑ709 basic amplifier circuits                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | 4.1                                                                                                  | Introduction                                                                                                                                                                                                                                                                                                                                                                        |

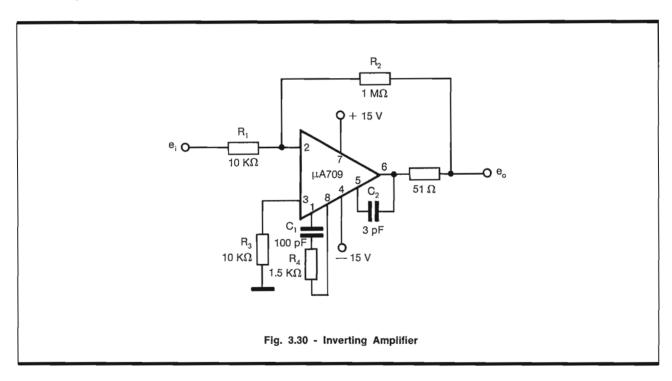

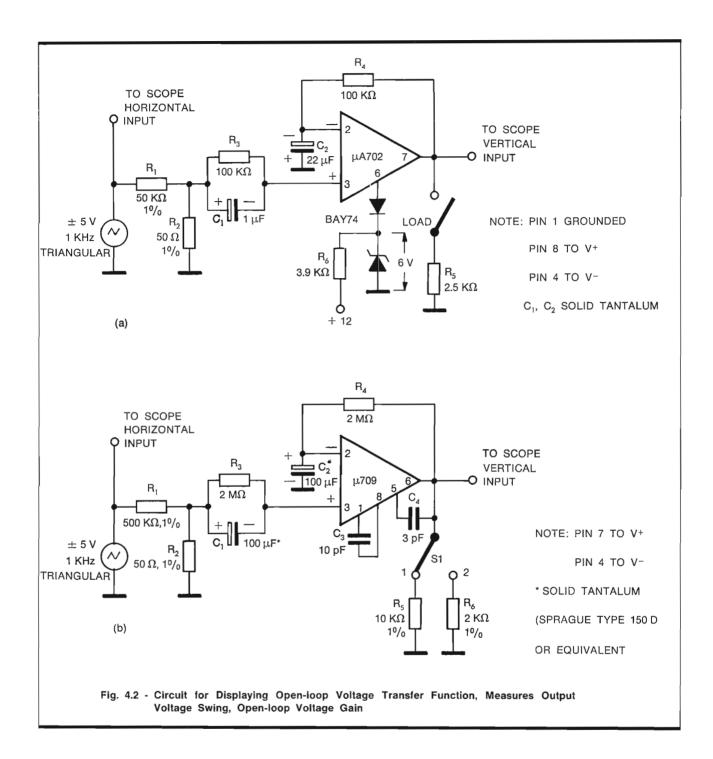

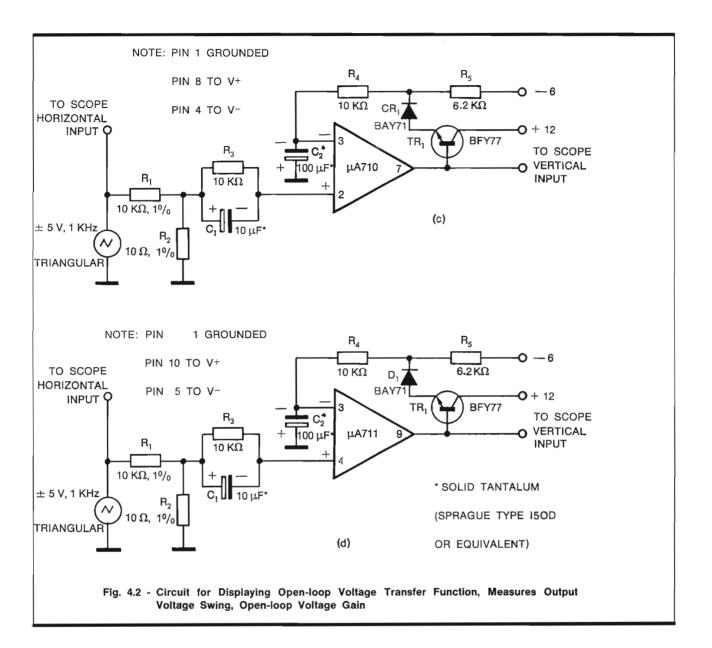

| 3.3.1                                                                                                                                                                    | Inverting amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         | 4.2                                                                                                  | Test circuits                                                                                                                                                                                                                                                                                                                                                                       |

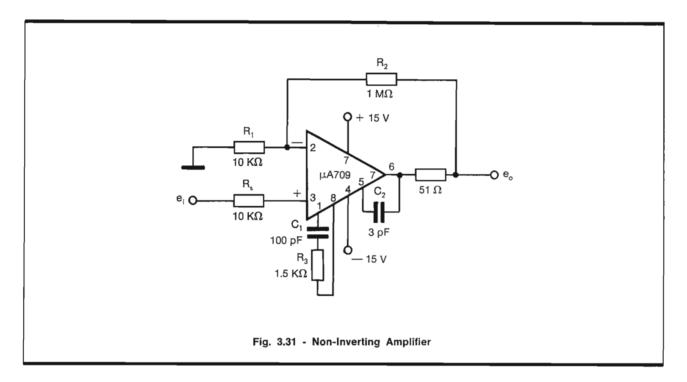

| 3.3.2                                                                                                                                                                    | Non-inverting amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | 4.2.1                                                                                                | General functional test                                                                                                                                                                                                                                                                                                                                                             |

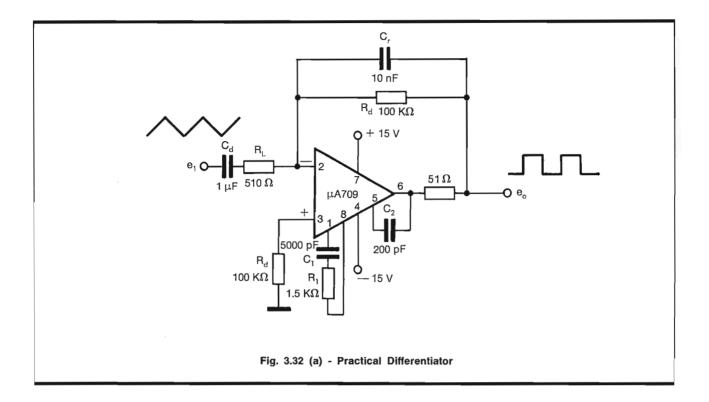

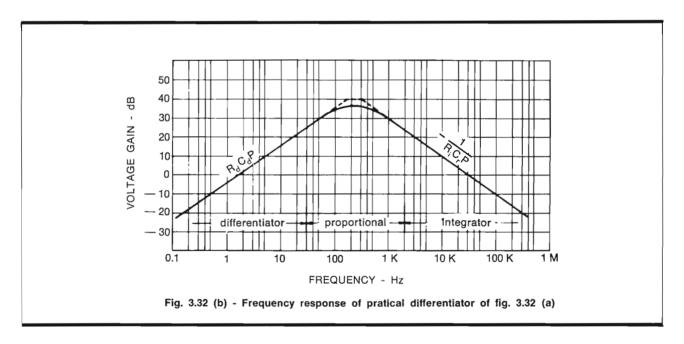

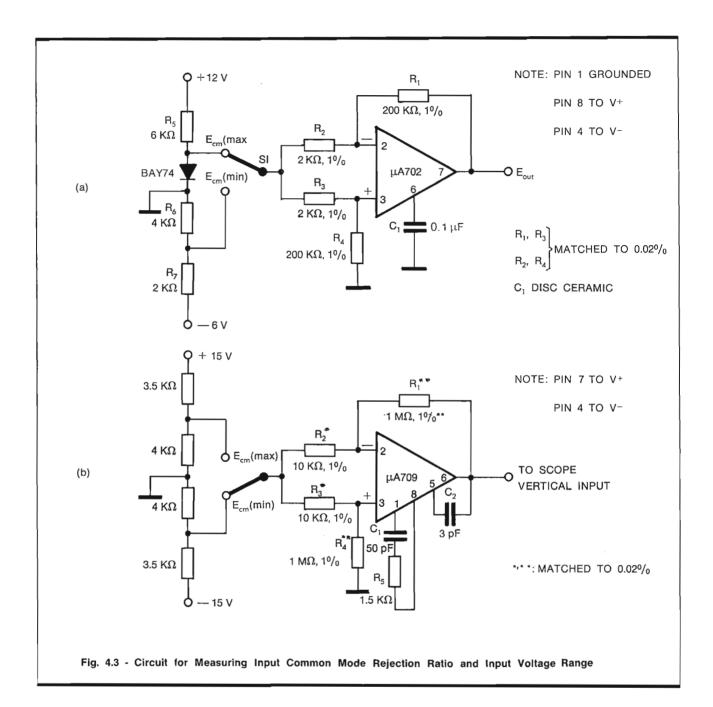

| 3.3.3                                                                                                                                                                    | Differentiator                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         | 4.2.2                                                                                                | Common-mode rejection ratio                                                                                                                                                                                                                                                                                                                                                         |

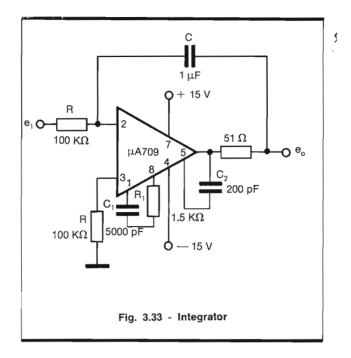

| 3.3.4                                                                                                                                                                    | Integrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |                                                                                                      | and input voltage range                                                                                                                                                                                                                                                                                                                                                             |

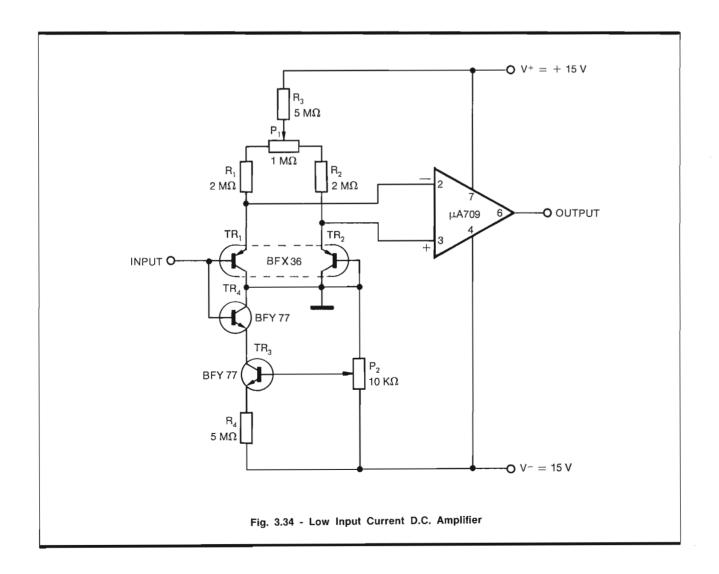

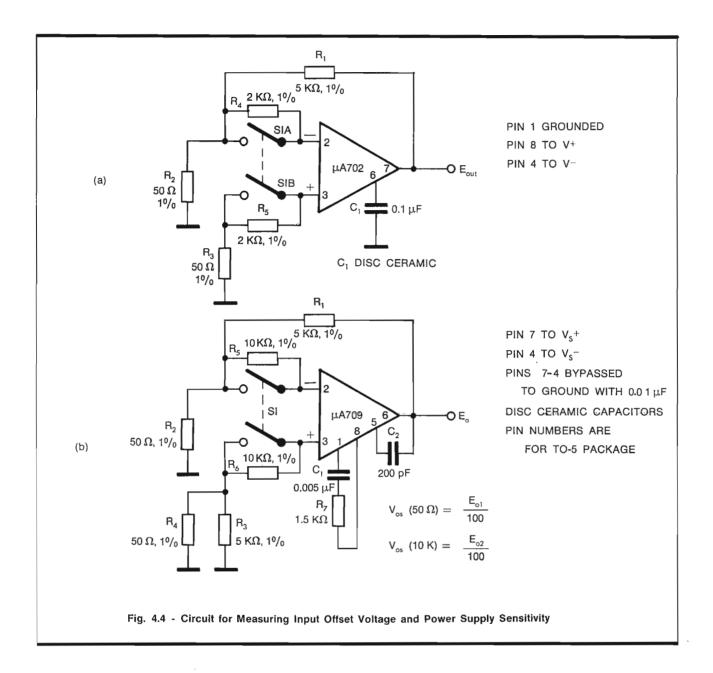

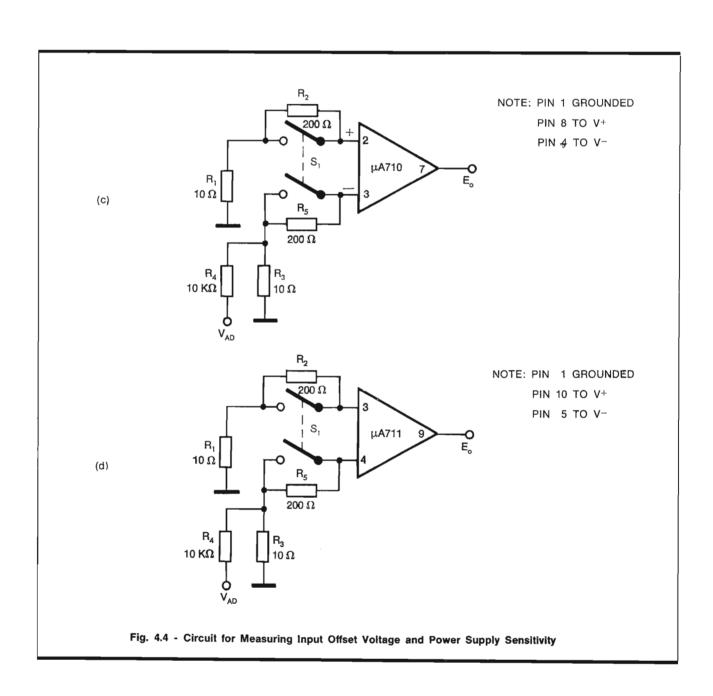

| 3.3.5                                                                                                                                                                    | Low input current D.C. amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | 4.2.3                                                                                                | Input offset voltage                                                                                                                                                                                                                                                                                                                                                                |

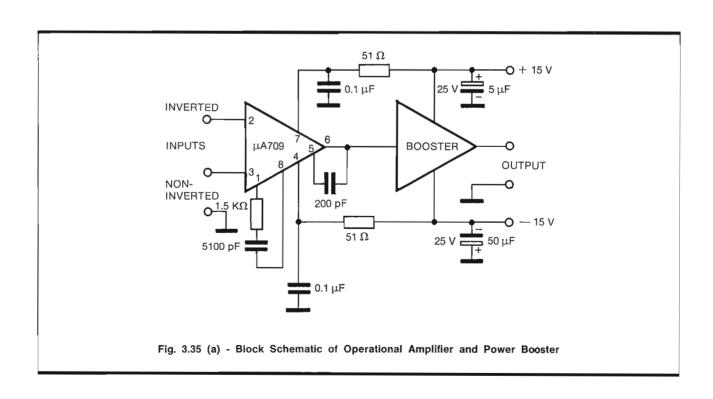

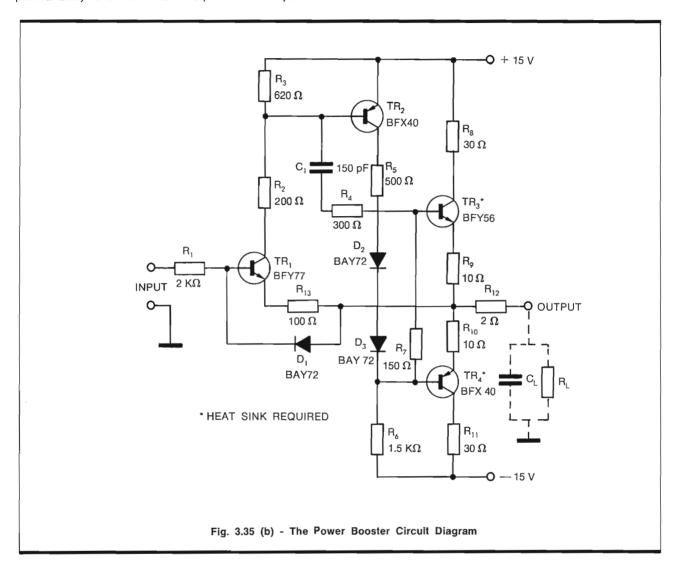

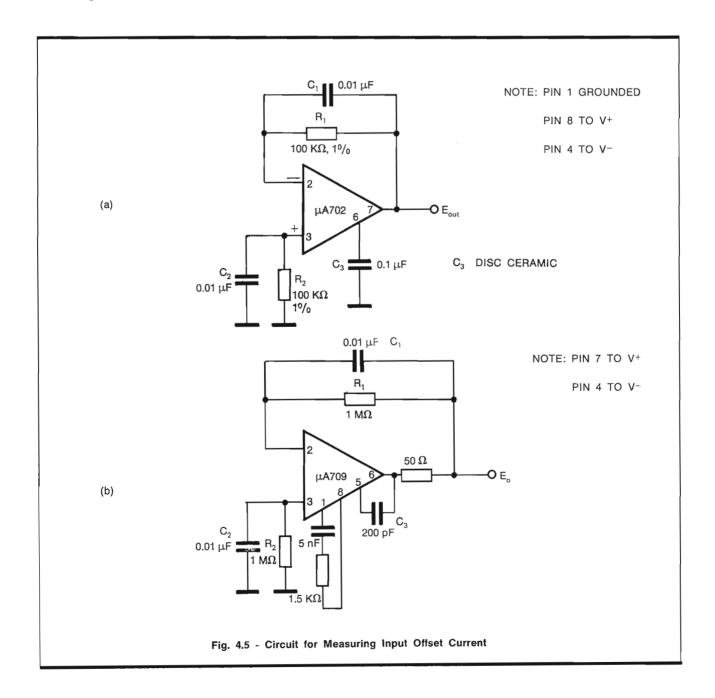

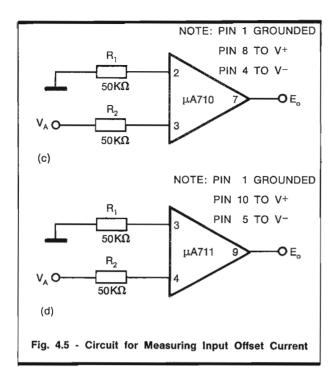

| 3.3.6                                                                                                                                                                    | Power booster amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         | 4.2.4                                                                                                | Input offset current                                                                                                                                                                                                                                                                                                                                                                |

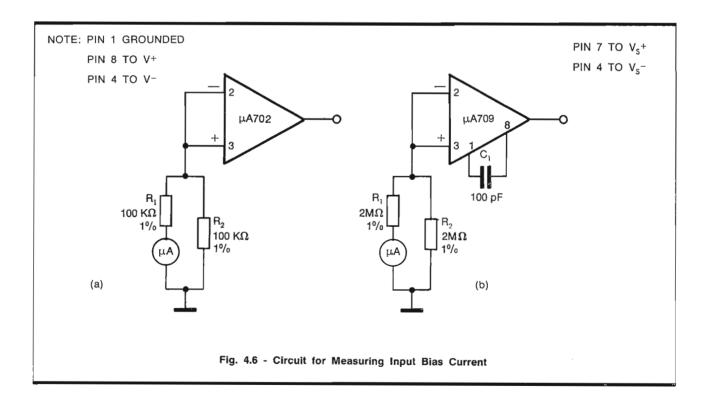

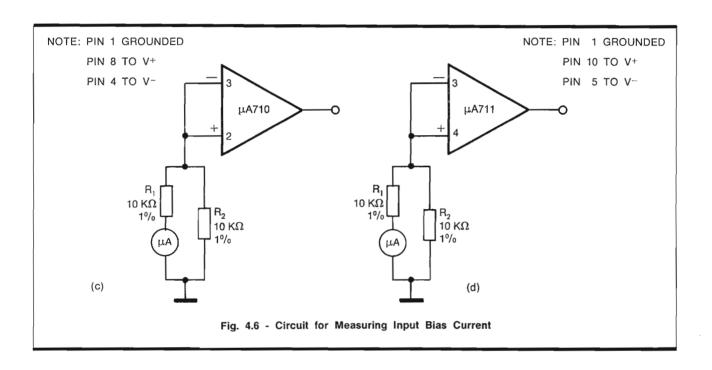

|                                                                                                                                                                          | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         | 4.2.5                                                                                                | Input bias current                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                          | Balana II and a sure a supervise                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                     |

| 3.4                                                                                                                                                                      | Miscellaneous circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         | 4.2.6                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                   |

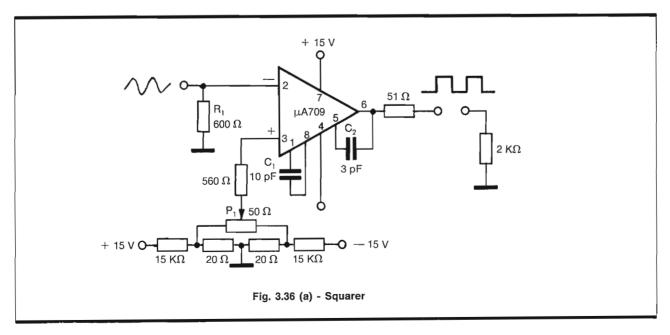

| 3.4.1                                                                                                                                                                    | Squarer circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         | 4.2.6                                                                                                | Supply voltage rejection ratio                                                                                                                                                                                                                                                                                                                                                      |

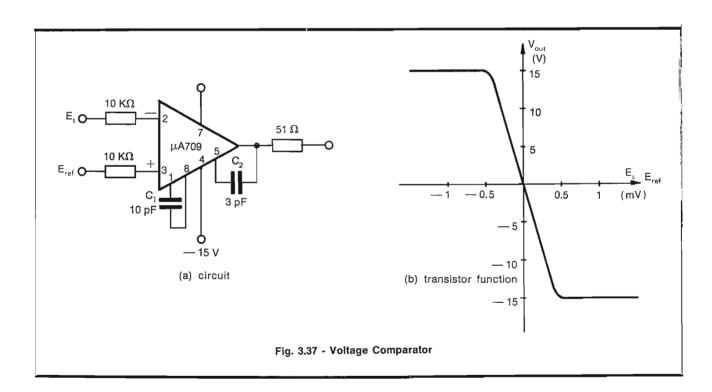

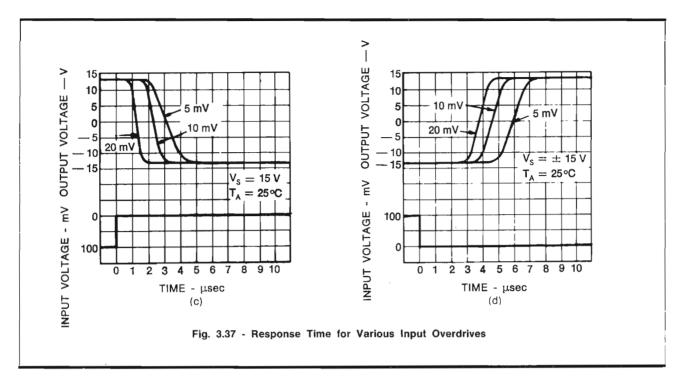

|                                                                                                                                                                          | Squarer<br>Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         | 4.2.6                                                                                                | •                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.4.1                                                                                                                                                                    | Squarer                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0 1     |                                                                                                      | Supply voltage rejection ratio                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.1<br>3.4.2                                                                                                                                                           | Squarer<br>Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Section |                                                                                                      | •                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                                                                                         | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator                                                                                                                                                                                                                                                                                                                                                                                                  | Section | 5                                                                                                    | Supply voltage rejection ratio  FREQUENCY COMPENSATION                                                                                                                                                                                                                                                                                                                              |

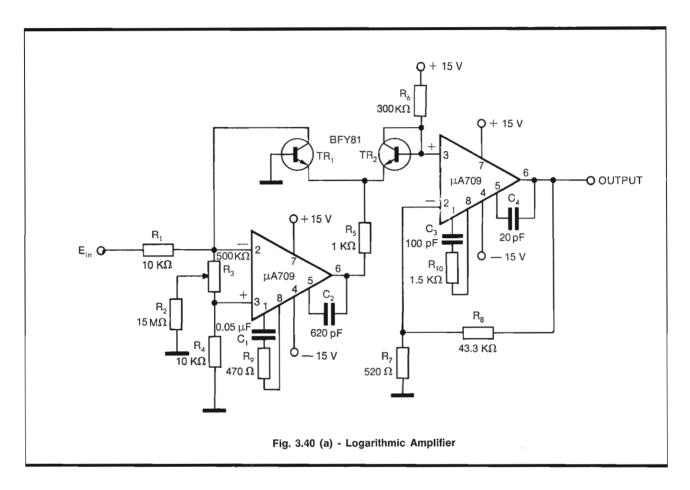

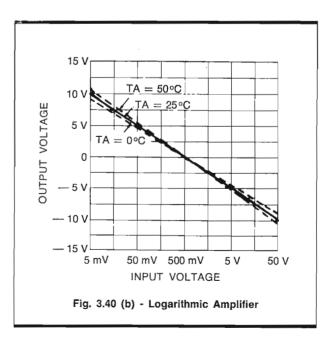

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                                                                                         | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier                                                                                                                                                                                                                                                                                                                                                                            | Section |                                                                                                      | Supply voltage rejection ratio                                                                                                                                                                                                                                                                                                                                                      |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4                                                                                                                                         | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator                                                                                                                                                                                                                                                                                                                                                                                                  | Section | 5                                                                                                    | Supply voltage rejection ratio  FREQUENCY COMPENSATION  General                                                                                                                                                                                                                                                                                                                     |

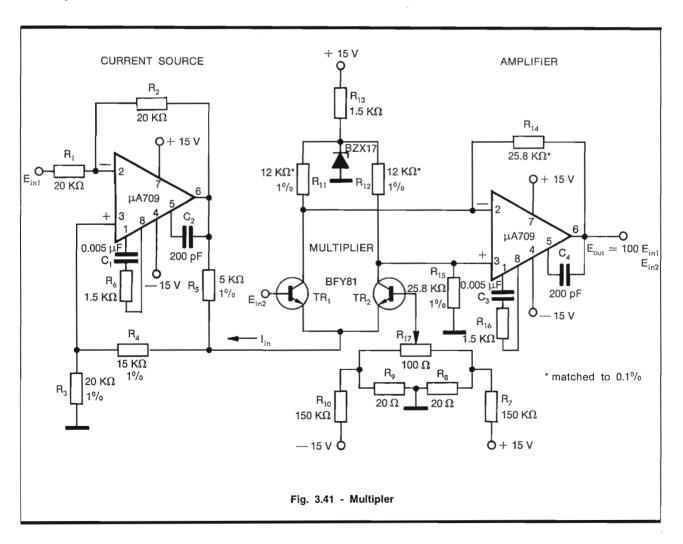

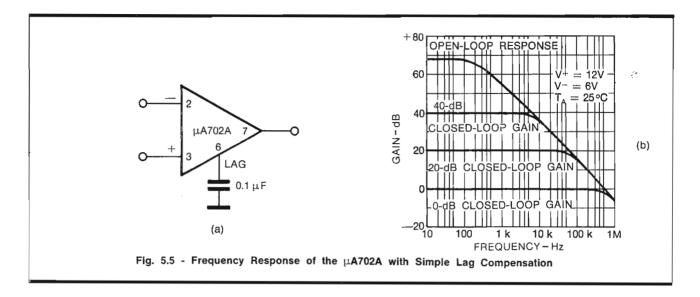

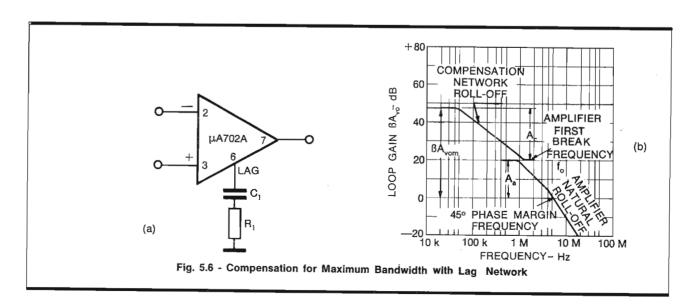

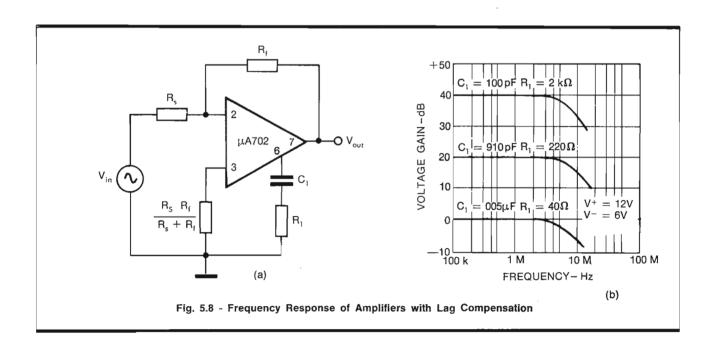

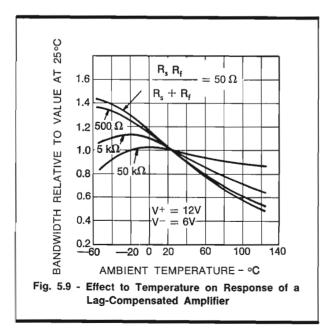

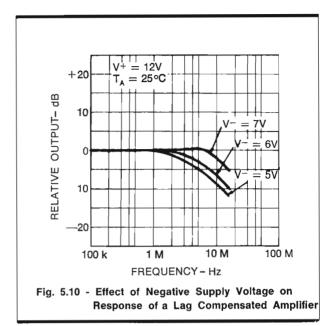

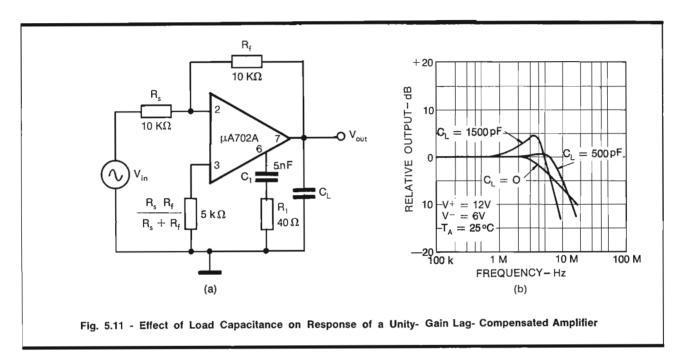

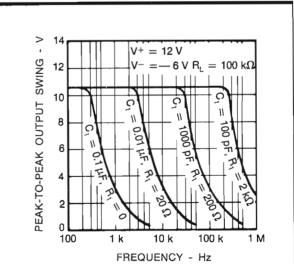

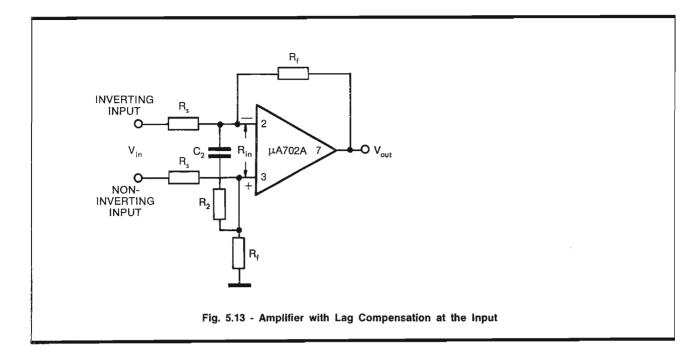

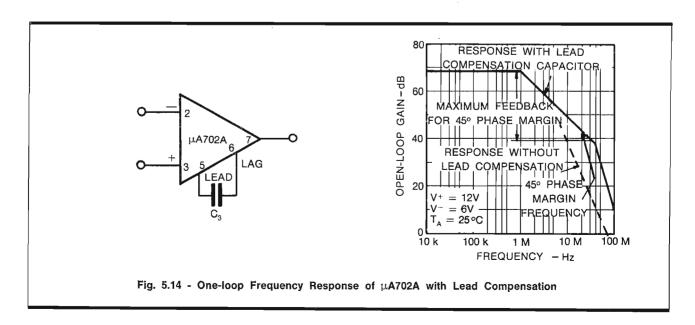

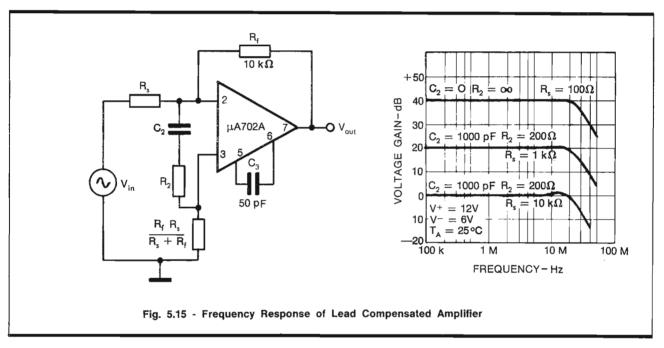

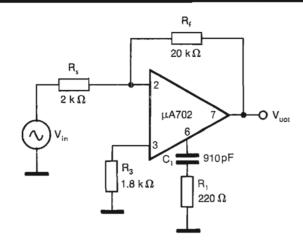

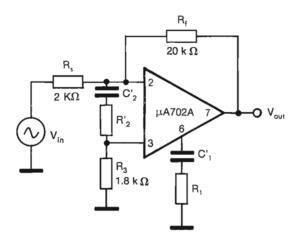

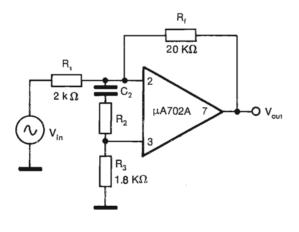

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5                                                                                                                                | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier                                                                                                                                                                                                                                                                                                                                                                            | Section | 5<br>5.1<br>5.2                                                                                      | Supply voltage rejection ratio  FREQUENCY COMPENSATION  General  µA702A operational amplifier                                                                                                                                                                                                                                                                                       |

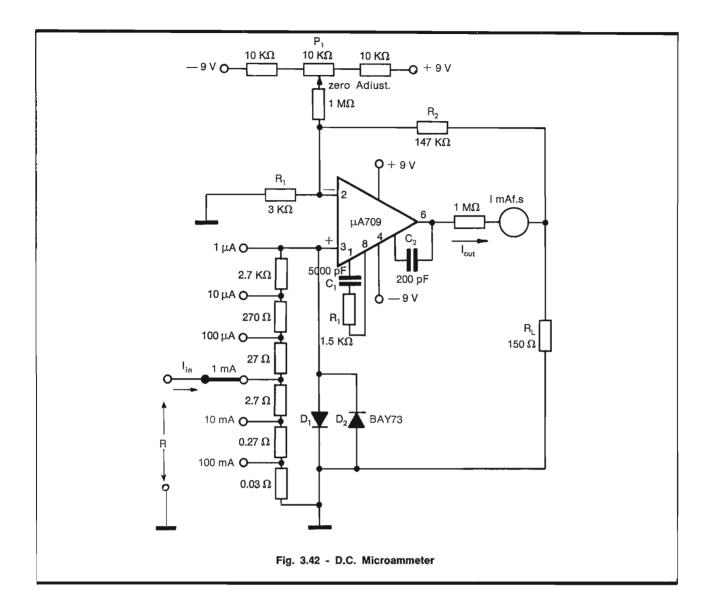

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7                                                                                                              | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter                                                                                                                                                                                                                                                                                                                                                    | Section | 5<br>5.1<br>5.2<br>5.2.1                                                                             | Supply voltage rejection ratio  FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation                                                                                                                                                                                                                                                                     |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7                                                                                                              | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits                                                                                                                                                                                                                                                                                                                   | Section | 5<br>5.1<br>5.2<br>5.2.1<br>5.2.2                                                                    | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation                                                                                                                                                                                                                                                                             |

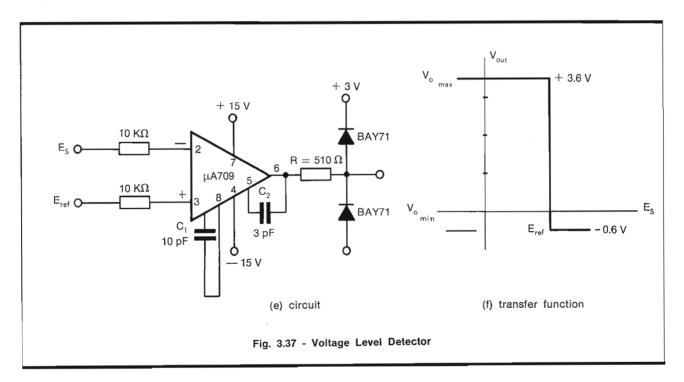

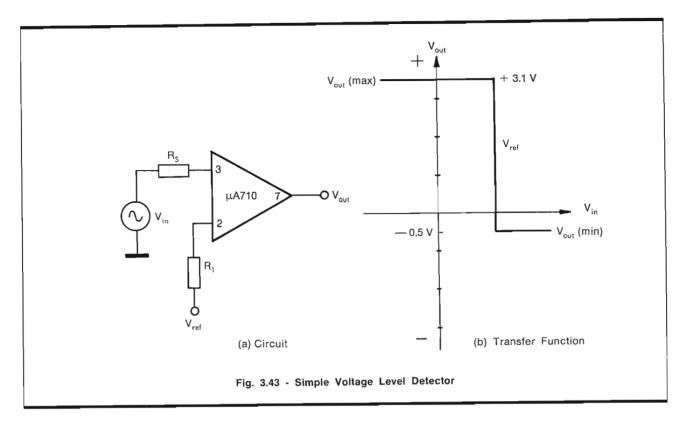

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1                                                                                       | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector                                                                                                                                                                                                                                                                                     | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3                                                                | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation                                                                                                                                                                                                                                                          |

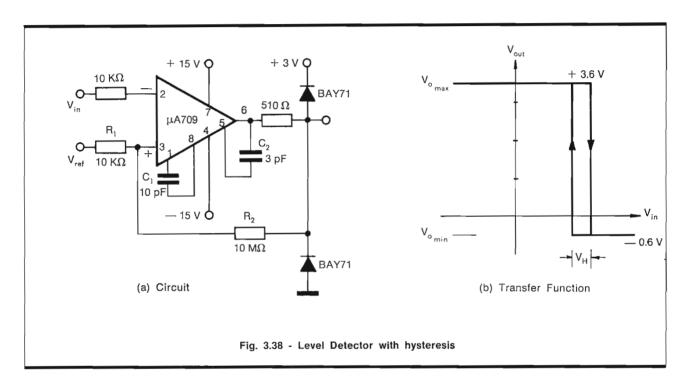

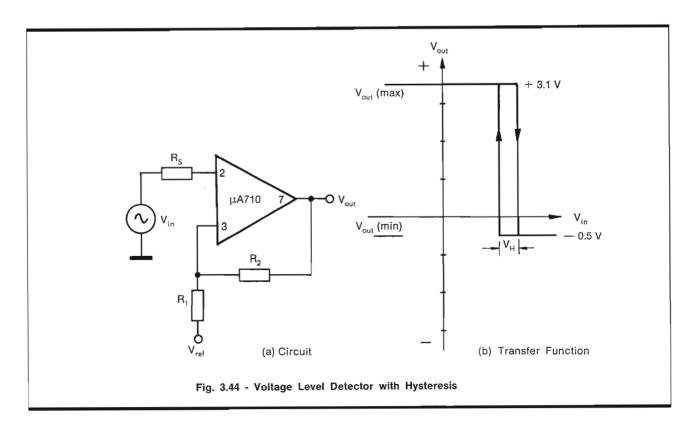

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1                                                                                       | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with                                                                                                                                                                                                                                                         | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                                       | FREQUENCY COMPENSATION  General                                                                                                                                                                                                                                                                                                                                                     |

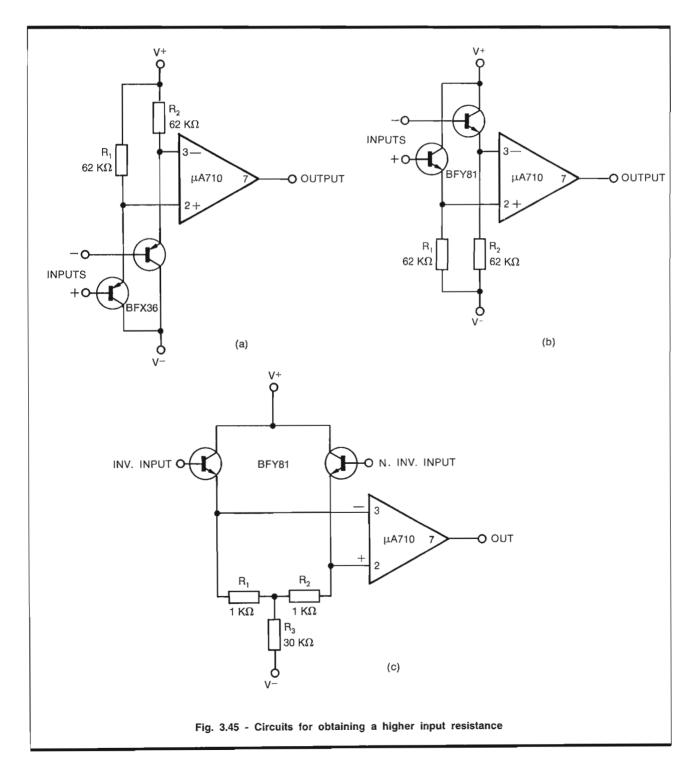

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1                                                                                       | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis                                                                                                                                                                                                                                              | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3                                                                | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise                                                                                                                                                                                                           |

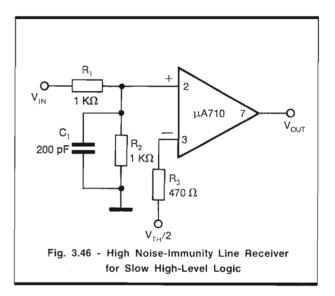

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1                                                                                       | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher                                                                                                                                                                                                             | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                              | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise considerations                                                                                                                                                                                            |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3                                                                     | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance                                                                                                                                                                                            | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4                                                       | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise                                                                                                                                                                                                           |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3                                                                     | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter   A710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers                                                                                                                                                                             | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5                                              | FREQUENCY COMPENSATION  General                                                                                                                                                                                                                                                                                                                                                     |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3                                                                     | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance                                                                                                                                                                                            | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3                              | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise  considerations  Special precautions  µA709 operational amplifier                                                                                                                                         |

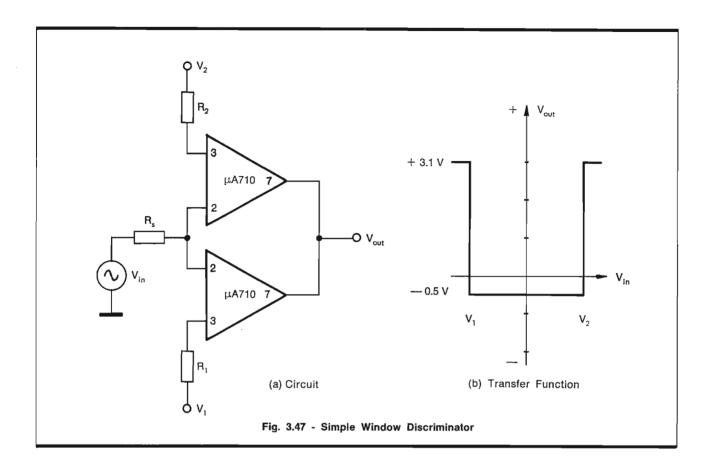

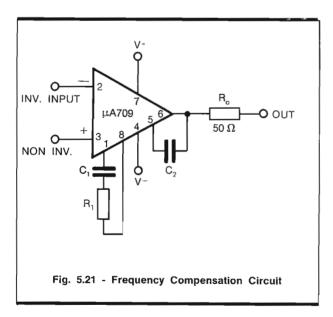

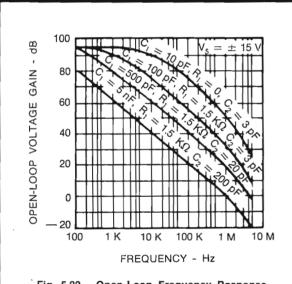

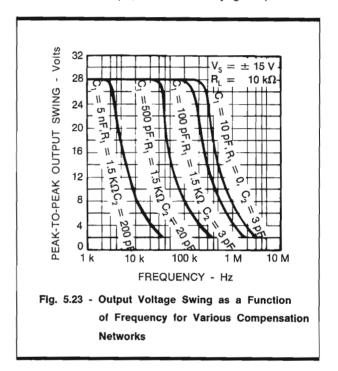

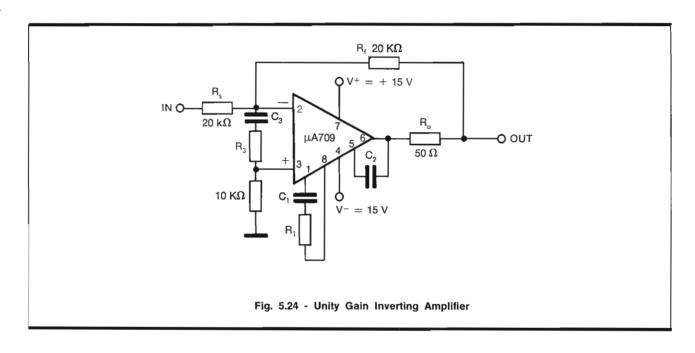

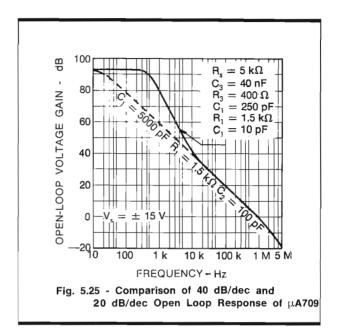

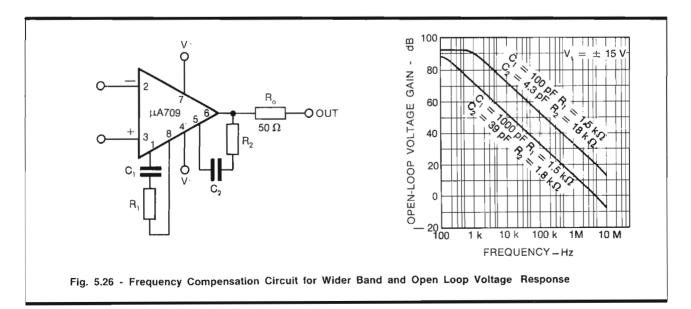

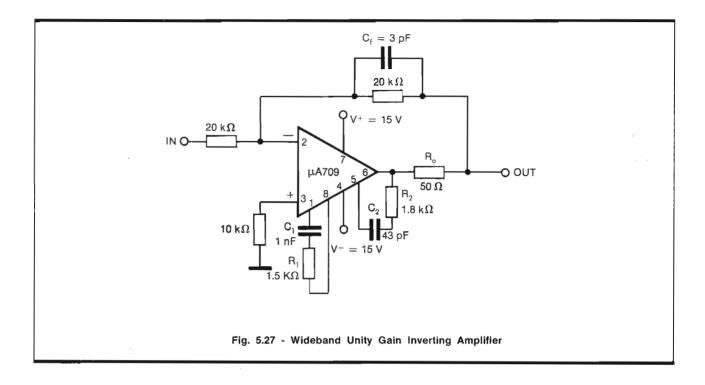

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5                                                   | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator                                                                                                                                                 | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1                            | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise  considerations  Special precautions  µA709 operational amplifier  Lag compensation                                                                                                                       |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3                                                                     | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator  Miscellaneous circuits                                                                                                                         | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2                   | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise  considerations  Special precautions  µA709 operational amplifier  Lag compensation  Input lag compensation  Input lag compensation                                                                       |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br><b>3.6</b>                                     | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter     A710 basic comparator circuits Simple voltage level detector Voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator  Miscellaneous circuits using                                                                                          | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2<br>5.3.3          | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise  considerations  Special precautions  µA709 operational amplifier  Lag compensation  Input lag compensation  Input lag compensation  Input lag compensation  Intermediate frequency compensation          |

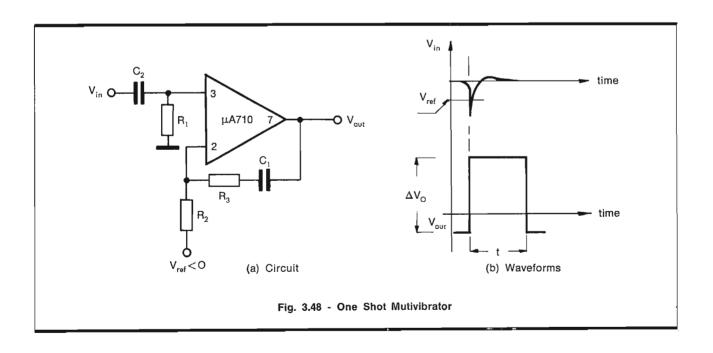

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br><b>3.6</b>                                     | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator  Miscellaneous circuits using µA710 One-shot multivibrator                                                                                      | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2                   | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise  considerations  Special precautions  µA709 operational amplifier  Lag compensation  Input lag compensation  Input lag compensation  Intermediate frequency compensation  Frequency response with a slope |

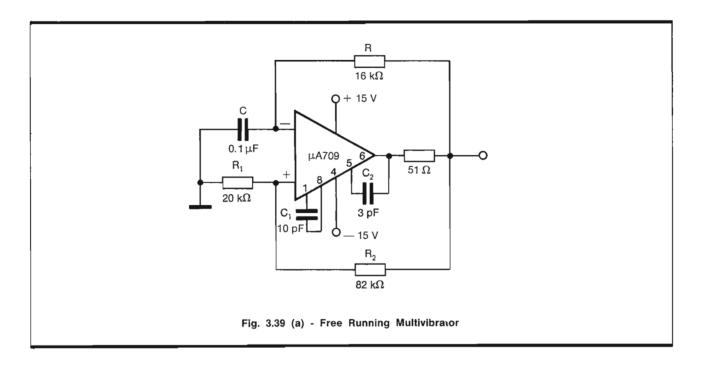

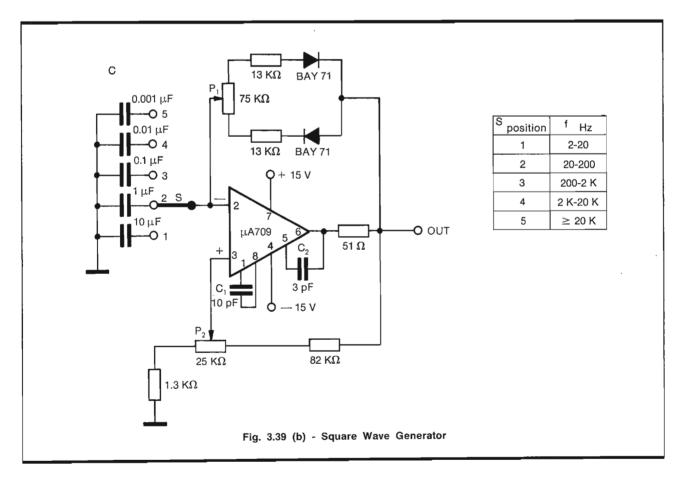

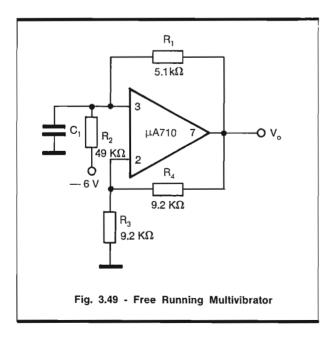

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br><b>3.6</b>                                     | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator  Miscellaneous circuits using µA710 One-shot multivibrator Free-running multivibrator                                    | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | FREQUENCY COMPENSATION  General                                                                                                                                                                                                                                                                                                                                                     |

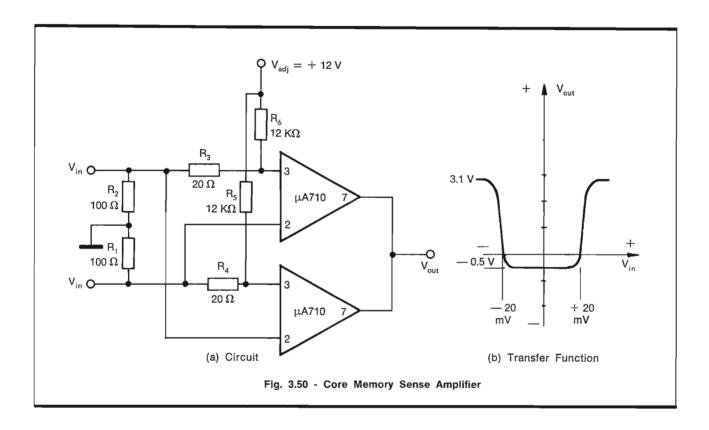

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.6.1<br>3.6.2<br>3.6.3                               | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator  Miscellaneous circuits using µA710 One-shot multivibrator Free-running multivibrator Core-memory sense amplifier                               | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2<br>5.3.3          | FREQUENCY COMPENSATION  General  µA702A operational amplifier  Lag compensation  Input lag compensation  Lead compensation  Other circuits  « Slewing » rate versus noise  considerations  Special precautions  µA709 operational amplifier  Lag compensation  Input lag compensation  Input lag compensation  Intermediate frequency compensation  Frequency response with a slope |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br><b>3.5</b><br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br><b>3.6</b><br>3.6.1<br>3.6.2<br>3.6.3<br>3.6.4 | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator  Miscellaneous circuits using µA710 One-shot multivibrator Free-running multivibrator Core-memory sense amplifier Crystal-controlled oscillator | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | FREQUENCY COMPENSATION  General                                                                                                                                                                                                                                                                                                                                                     |

| 3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.6<br>3.4.7<br>3.5<br>3.5.1<br>3.5.2<br>3.5.3<br>3.5.4<br>3.5.5<br>3.6.1<br>3.6.2<br>3.6.3                               | Squarer Comparator Voltage comparator with hysteresis Astable multivibrator Logarithmic amplifier Multiplier Microammeter  µA710 basic comparator circuits Simple voltage level detector Voltage level detector with hysteresis Circuits used to obtain a higher input resistance Line receivers Simple Window discriminator  Miscellaneous circuits using µA710 One-shot multivibrator Free-running multivibrator Core-memory sense amplifier                               | Section | 5.1<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.3.1<br>5.3.2<br>5.3.3<br>5.3.4 | FREQUENCY COMPENSATION  General                                                                                                                                                                                                                                                                                                                                                     |

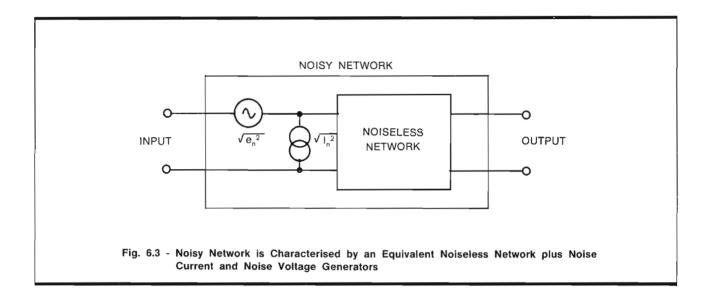

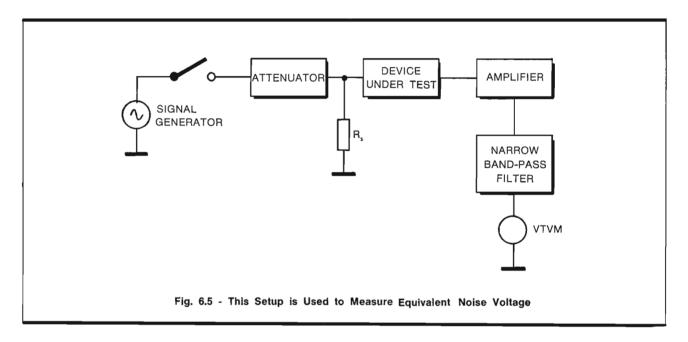

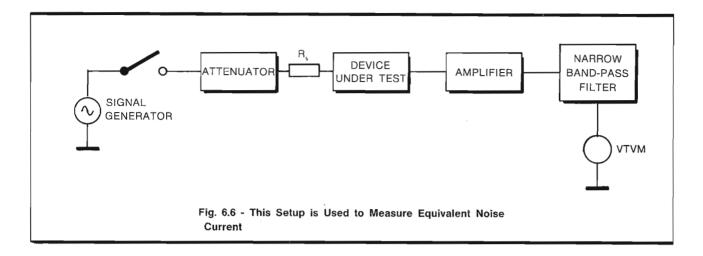

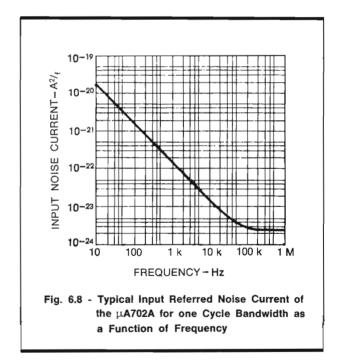

| Section | 6     | NOISE                                         |         | 6.2.2 | Integrated noise characteristics   |  |

|---------|-------|-----------------------------------------------|---------|-------|------------------------------------|--|

|         | 6.1   | General                                       |         |       | of the µA702A                      |  |

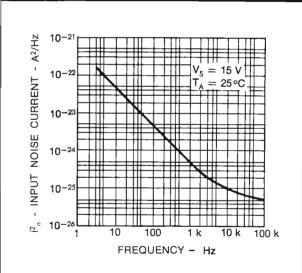

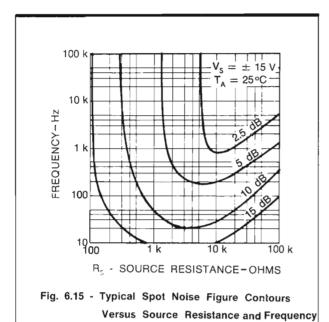

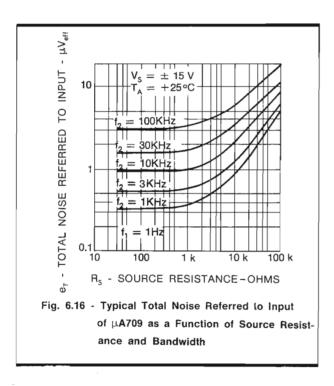

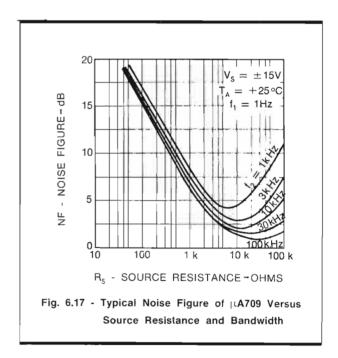

|         | 6.1.1 | Introduction                                  |         | 6.3   | Noise characteristics of the µA709 |  |

|         | 6.1.2 | Noise terminology                             |         | 6.3.1 | Noise characteristics as a         |  |

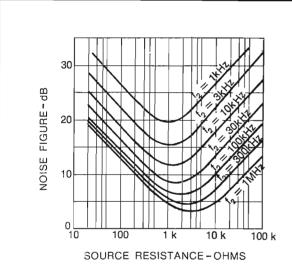

|         | 6.1.3 | An amplifier considered as a                  |         |       | function of frequency              |  |

|         |       | four-pole network                             |         | 6.3.2 | Integrated noise characteristics   |  |

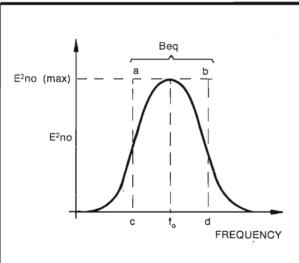

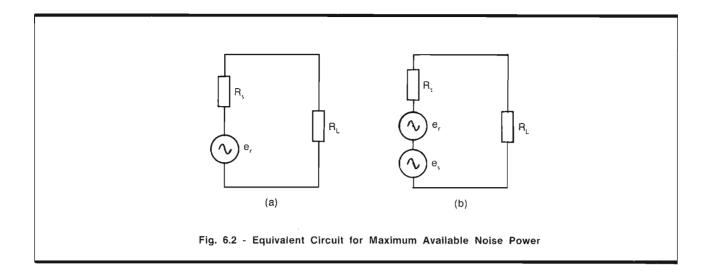

|         | 6.1.4 | Evaluation of the integrated noise            |         |       | of the µA709                       |  |

|         |       | factor for a four-pole network                |         |       | •                                  |  |

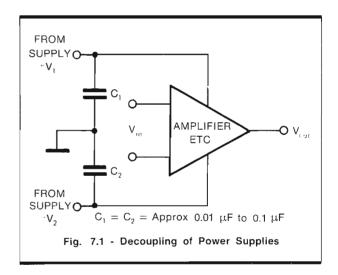

|         | 6.1.5 | Noise voltage and current measurement methods | Section | 7     | POWER SUPPLIES                     |  |

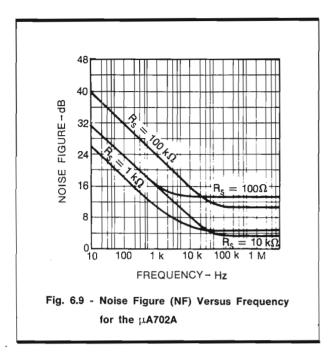

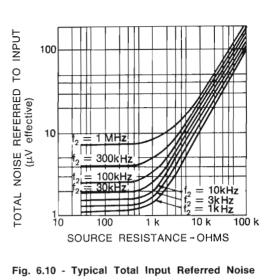

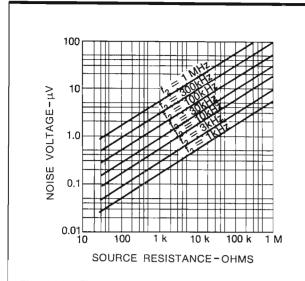

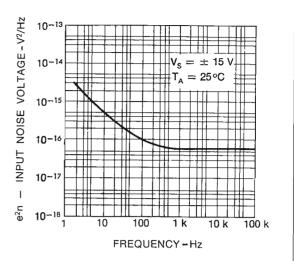

|         | 6.2   | Noise characteristics of the µA702A           |         | 7.1   | General                            |  |

|         | 6.2.1 | Noise characteristics as a                    |         | 7.1.1 | Introduction                       |  |

|         |       | function of frequency                         |         | 7.1.2 | Mandatory characteristics          |  |

### 1. INTRODUCTION

#### 1.1 PURPOSE OF HANDBOOK

This Handbook has been produced so as to bring under one cover as much information as possible likely to be of use to Systems and Electronic Design engineers who are contemplating using linear integrated circuits from the SGS family to solve their specific circuit problems.

Where possible, practical circuits have been included with actual component values but, due to the many applications that are possible, supplementary notes are included, giving explanations for the design values. By this means, and with the additional information available under the more general headings of Frequency Compensation, Noise, Power Supplies etc., it is hoped that the engineer will be in a position to adapt these circuits to his own requirements.

The Sections on basic amplifier circuits have been added for the benefit of engineers newly entering the field of operational amplifier usage.

#### 1.2 INSTRUCTIONS FOR HANDBOOK USAGE

It will be noted that the contents are divided into Sections and sub-Sections which are identified by means of a two or three digit code.

The location of any the specified material shown in the "List of Contents" pages can therefore be readily found. The date of issue is indicated at the foot of the second page.

The Company should be consulted to obtain the latest information available concerning the Linear Integrated Circuit family.

Unless otherwise specifically stated, the pin numbers shown in various circuit diagrams refer to the TO-5 package. For the connections applicable to other alternative packages, the appropriate data sheet should be consulted.

precautions to ensure that no patent infringement can take place.

Whilst every effort has been made to obtain technical accuracy of the contents, the Company cannot assume liability for the possible consequences of adopting the circuits and component values described herein.

The circuit details and configurations described within this Handbook may be covered by various patent rights held by this Company or others. Publication of the information does not imply permission to use, or responsibility for usage of the circuit ideas presented without first taking precautions to ensure that no patent infringement can take place.

## 1.3 ECONOMICS OF INTEGRATED CIRCUITS COMPARED WITH DISCRETE-COMPONENT CIRCUITS

The technical advantages of integrated circuits are discussed in Section 2.1, but it is of interest to consider in general terms the economic factors which may affect the choice of whether integrated circuits are adopted for a particular design or not.

In the past, integrated circuits have been used mainly in designs where the prime concern was only to save weight or space. The additional bonus of reduced power consumption and extra reliability may have been of secondary importance. In these circumstances, the cost factor was not necessarily considered.

With improvements in the techniques for fabrication of integrated circuits, resulting in higher

yields and a steady reduction in price and also because new circuit designs are becoming available with a wider choice of operations with increasingly better performance, it is now possible to build up many systems where much of the electronics can be provided equally well by integrated circuits or discrete components. The choice in this case becomes an economic one.

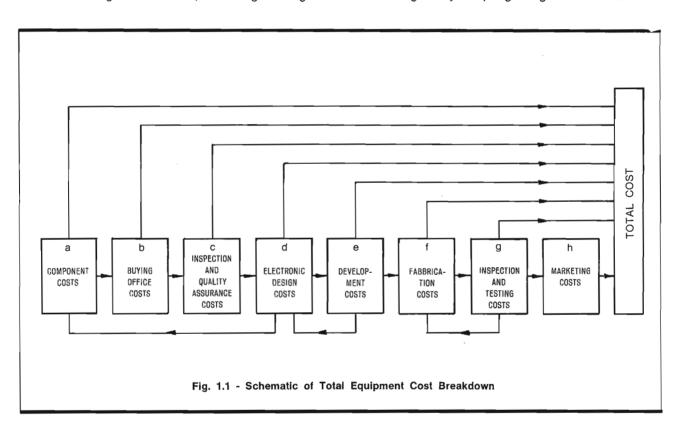

Fig. 1.1 is a simple diagrammatic representation of how the individual steps in manufacture of a piece of electronic equipment contribute to the total cost. Although both the circuit problems themselves and the internal organisation of the manufacturer building the equipment vary enormously, in very general terms it can be shown that, with the possible exception of item (a), the cost of each stage is reduced to some degree by adopting integrated circuits.

### COMPONENT COSTS

The cost of the individual item necessary to make a discrete-component Linear Circuit equivalent in performance to an Integrated Circuit is often more than the total cost of the integrated circuit itself. This is due to the relatively high cost of matched transistors and high-stability resistors usually required in this type of circuit.

### BUYING OFFICE COSTS

It is obvious that the organisation necessary to co-ordinate the purchase of quantities of individual components from a variety of manufacturers is comparatively costly, leaving aside the possibility of delayed delivery and its consequences on the production programme.

### INSPECTION AND QUALITY ASSURANCE

Here again, the costs attached to handling and testing a number of items is very heavy compared to that of an individual integrated circuit.

### ELECTRONIC DESIGN COSTS

In the design of both simple and complex systems, the overall man-hours spent on pure design are drastically reduced since integrated circuits can

provide guaranteed performances for well-defined circuit operations and environmental ranges.

### DEVELOPMENT COSTS

These are likely to be greatly reduced as well, for the same reasons that extensive development has already been carried out on the complete integrated circuit by the manufacturer, with the result that system performance can be more accurately predicted at the « paper work » stage. The necessity for circuit modification, which is always a difficult and costly procedure once production has started, is thus reduced to a minimum. In general, it is also often easier to carry out where integrated circuits have been used.

#### **FABRICATION COSTS**

Considerable saving in labour costs can be achieved by adopting integrated circuits. Both the materials (tag boards, sockets, heat-sinks, etc.) and the assembly time can be very much reduced. At the time of writing, an increasing number of manufacturers are offering low cost mounting facilities specifically designed for integrated circuits, with flexible interconnection system. The range of alternative packages offered by SGS, combined with a standardised mounting system adopted by a specific manufacturer, minimises the necessity for costly « one off » configurations. Systems containing many repetitive circuits have abvious additional advantages.

#### INSPECTION AND TESTING COSTS

At all levels this should be reduced, both because performance of integrated circuits is more predictable and parameter tolerances may be « designed out » at the initial stages and because interconnections, both soldered and by plug and socket, can be decimated. Analysis of system reliability shows that interconnection failures contribute significantly to the overall probability of system failure where discrete components are used.

### MARKETING

The utilisation of integrated circuits has reached a stage when the more sophisticated customer of an equipment manufacturer is beginning to expect the supplier to be incorporating integrated circuits in his designs.

In much the same way as, ten years ago, people were pointing out the advantages, of transistorisation so, today, integrated circuits are shown to be the next logical step forward.

The incorporation of integrated circuits manufactured by a Company whose reputation for performance and reliability is already well established can only help to increase confidence in the finished product.

### 2. DESIGNS FOR MONOLITHIC LINEAR INTEGRATED CIRCUITS

#### 2.1 DESIGN PHILOSOPHY

### 2.1.1 Integrated Circuits Compared with Discrete Components

The design of complete circuits (e.g. high-gain, general-purpose amplifiers), which are to be realised as integrated circuits rather than made up from separate components, requires a new concept in the basic approach. This is due not only to certain limitations inherent in integrated manufacturing techniques but also because of new design freedoms that it allows.

In general, it is true to say that the total cost of a discrete component circuit is directly proportional to the number of transistors, capacitors and resistors in descending order of importance. PNP or NPN transistors may be used at will, but matching of separate transistors for gain,  $V_{\text{BE}}$ , etc., incurs considerable cost penalties while the necessity for specifying certain resistor values to close tolerance does not have the same significance.

With integrated circuits, it is possible to diffuse in both NPN and PNP devices, but for ease of manufacture, it is generally preferred to keep to NPN exclusively, for the more simple circuits. With integrated circuits there is more freedom in the number of active three-layer or two-layer junctions wich may be used. This is because doubling the number of such junctions (with the proviso that no extra processes are involved and that the overall yield is not significantly reduced) will certainly not increase the cost proportionally. Existing techniques by which resistors are formed makes it impractical to gua-